successivo

precedente

inizio

fine

indice generale

aiuto

indice analitico

volume

parte

TXT

HTML

PDF

pdf

gdoc

P4

Flip-flop

I circuiti combinatori hanno la caratteristica di fornire un certo valore di uscita, unicamente sulla base dei valori presenti in ingresso, anche se la formazione del valore di uscita richiede comunque un piccolo lasso di tempo, rispetto alla disponibilità dei dati di partenza. Pertanto, si dice che i circuiti combinatori non hanno memoria, in quanto non tengono conto di ciò che è avvenuto in precedenza. Al contrario, un circuito sequenziale, tiene conto della dinamica con cui provengono i dati in ingresso, mantenendo uno stato, dal quale dipendono gli effetti dei cambiamenti successivi dei dati in ingresso.

I circuiti sequenziali si basano su componenti noti come memorie, le quali si realizzano attraverso i flip-flop. All'interno della categoria delle memorie, la documentazione scientifica e tecnica tende a usare il termine latch che si riferisce alla proprietà di questi circuiti di «scattare» da uno stato a un altro, riservando la definizione di flip-flop solo a un insieme ristretto di tali circuiti, in quanto avente caratteristiche più sofisticate. Tuttavia, qui si preferisce usare la qualifica di flip-flop per tutti questi circuiti, distinguendo di volta in volta il livello di sofisticazione di ogni variante.

Ritardo di propagazione

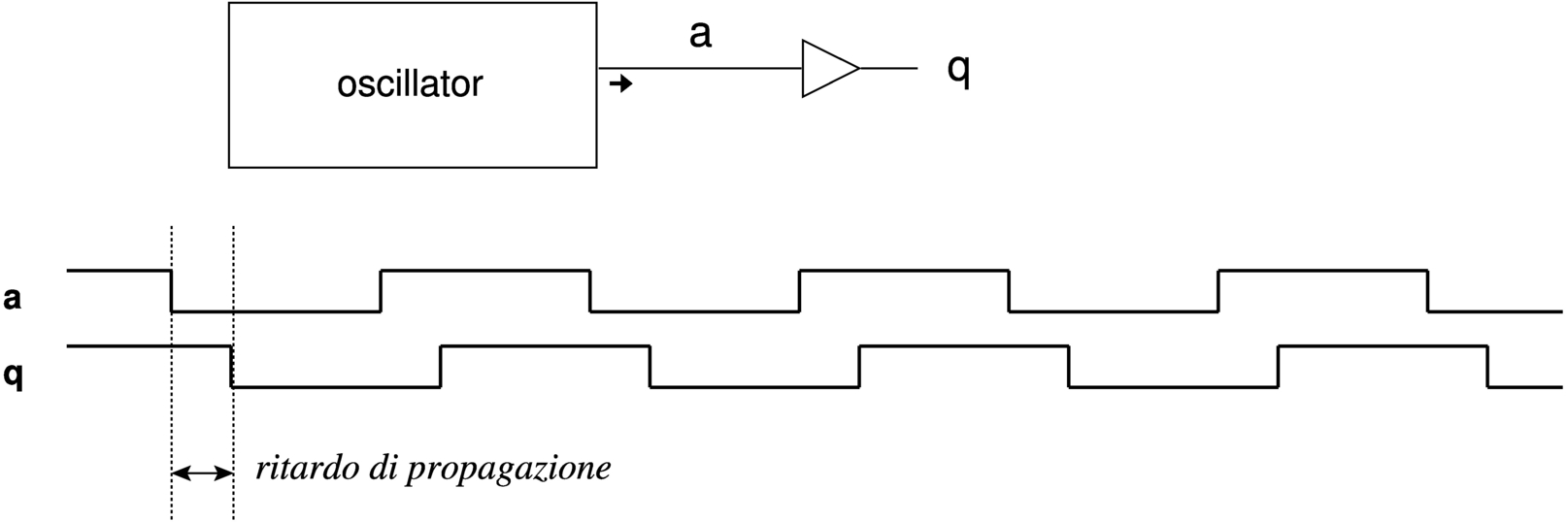

In un circuito combinatorio comune, perché l'uscita si adegui ai cambiamenti avvenuti in ingresso, si richiede un piccolo intervallo di tempo, noto come ritardo di propagazione. Questo ritardo dipende dalle caratteristiche fisiche e meccaniche del dispositivo con cui si realizza effettivamente il circuito combinatorio.

|

Figura u129.1. Esempio di ritardo nell'attraversamento di un buffer, ovvero di una porta logica non invertente: come si intende dallo schema, l'ingresso è pilotato da un oscillatore che produce un segnale alterno e nell'uscita si ottiene lo stesso segnale, ma leggermente ritardato.

|

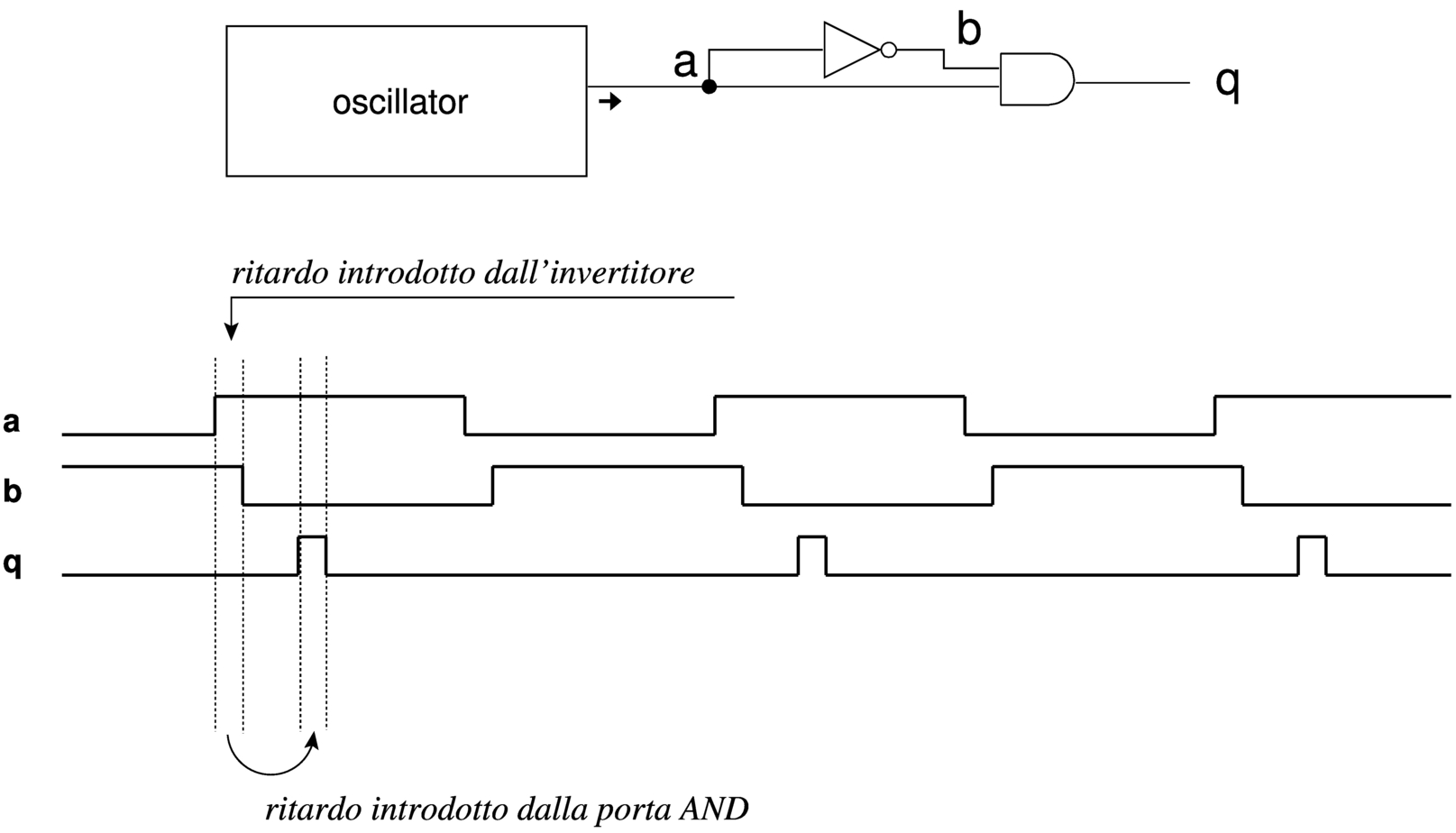

Il ritardo di propagazione si può sfruttare per ottenere un impulso molto breve, come si vede nella figura successiva.

|

Figura u129.2. Esempio di impulso generato sfruttando il ritardo di propagazione. In questo schema si intende che gli ingressi della porta AND siano bilanciati correttamente, nel senso che il cambiamento di stato da un ingresso o dall'altro, si rifletta sull'esito restituito nello stesso tempo.

|

Tabelle di verità

La tabella di verità è un modo con cui si rappresenta il comportamento di un circuito combinatorio, per cui si mostrano i valori in uscita come funzione dei valori in entrata, senza contare il ritardo di propagazione e la dinamica con cui si formano i dati in ingresso. Trattando invece di circuiti sequenziali, le tabelle di verità, ammesso che si utilizzino, vanno interpretate di volta in volta in base al contesto particolare. Nelle sezioni successive si introducono i flip-flop e nelle tabelle di verità si vuole considerare negli ingressi anche la variazione di stato; pertanto si usa la simbologia seguente:

| 0 | zero stazionario |

| _/¯ | variazione da zero a uno |

| 1 | uno stazionario |

| ¯\_ | variazione da uno a zero |

|

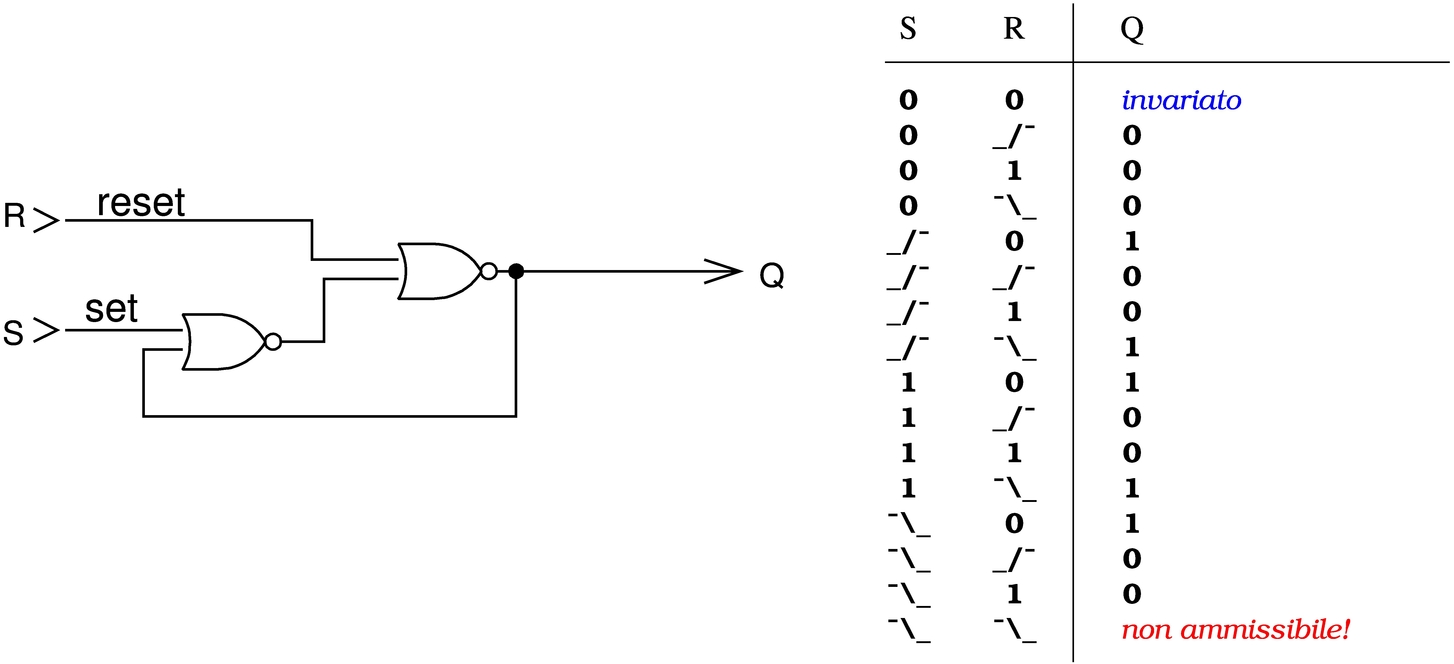

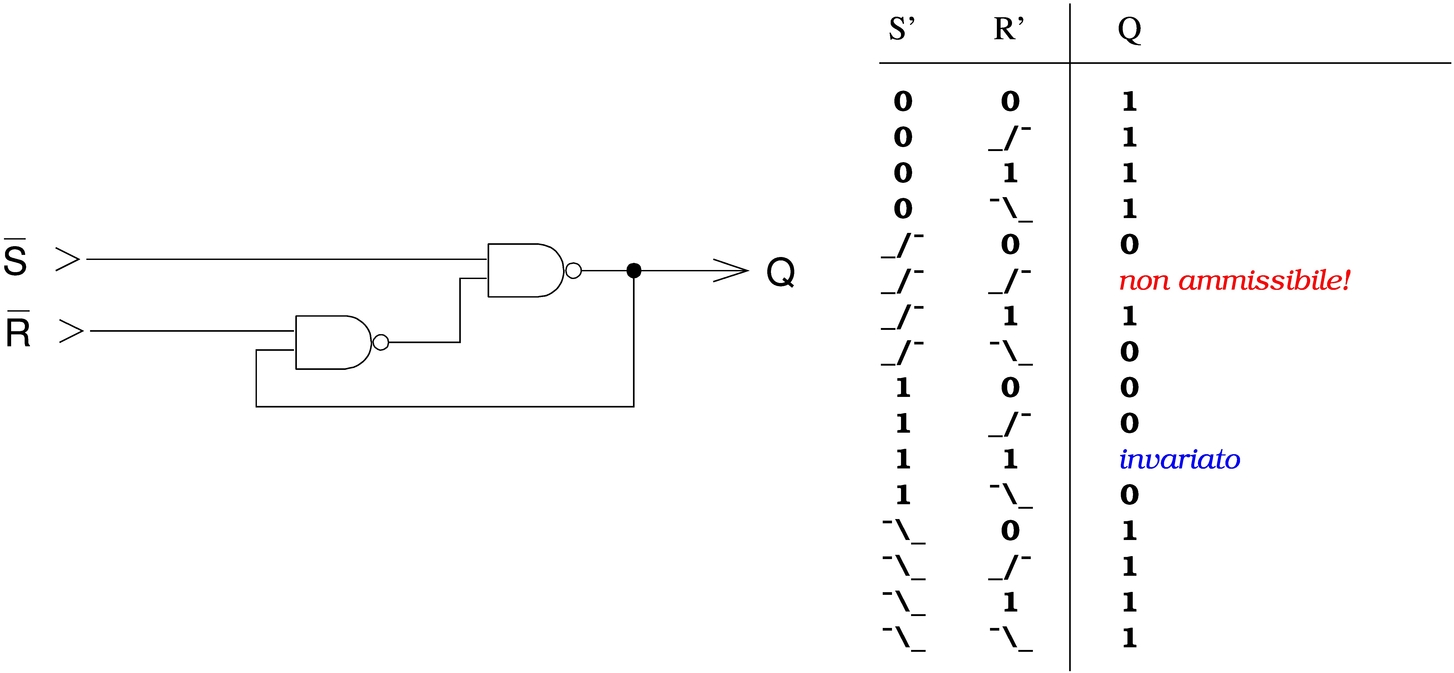

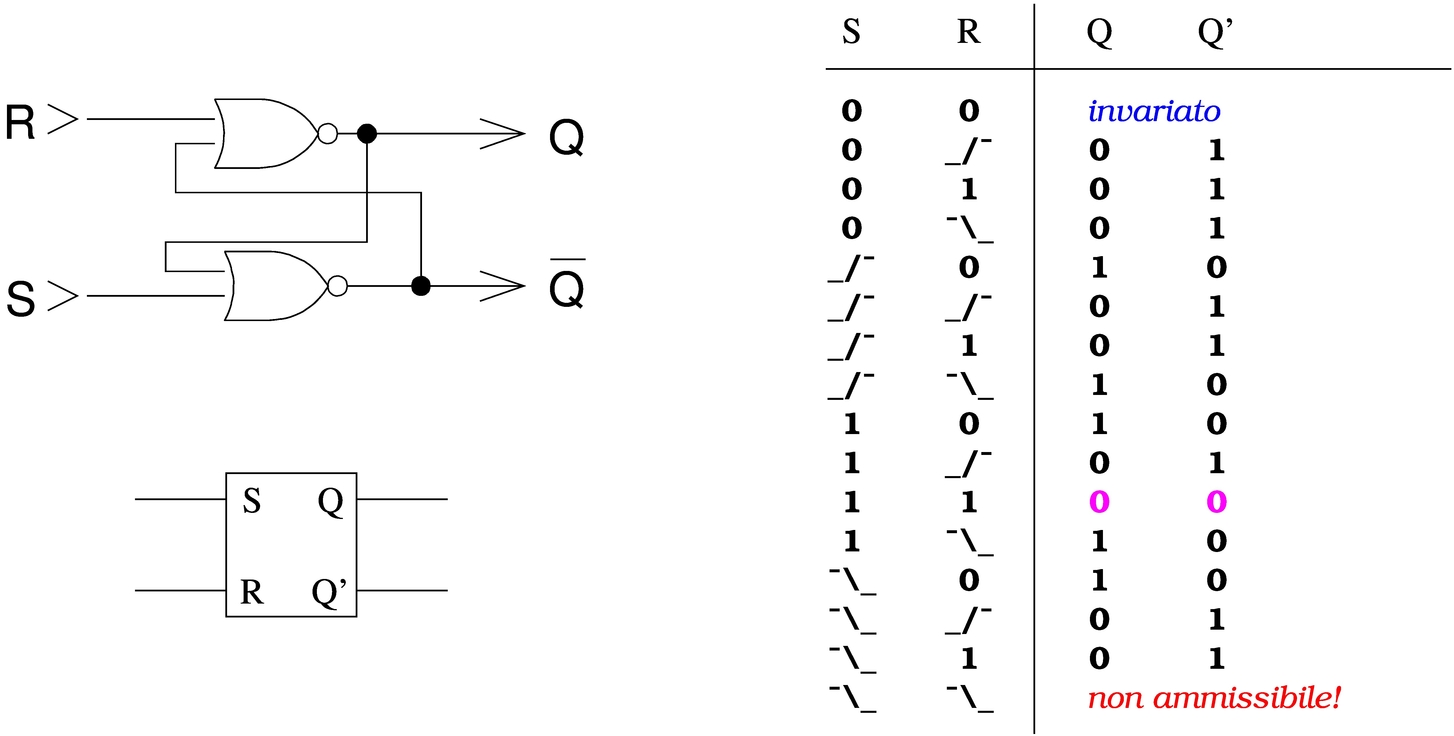

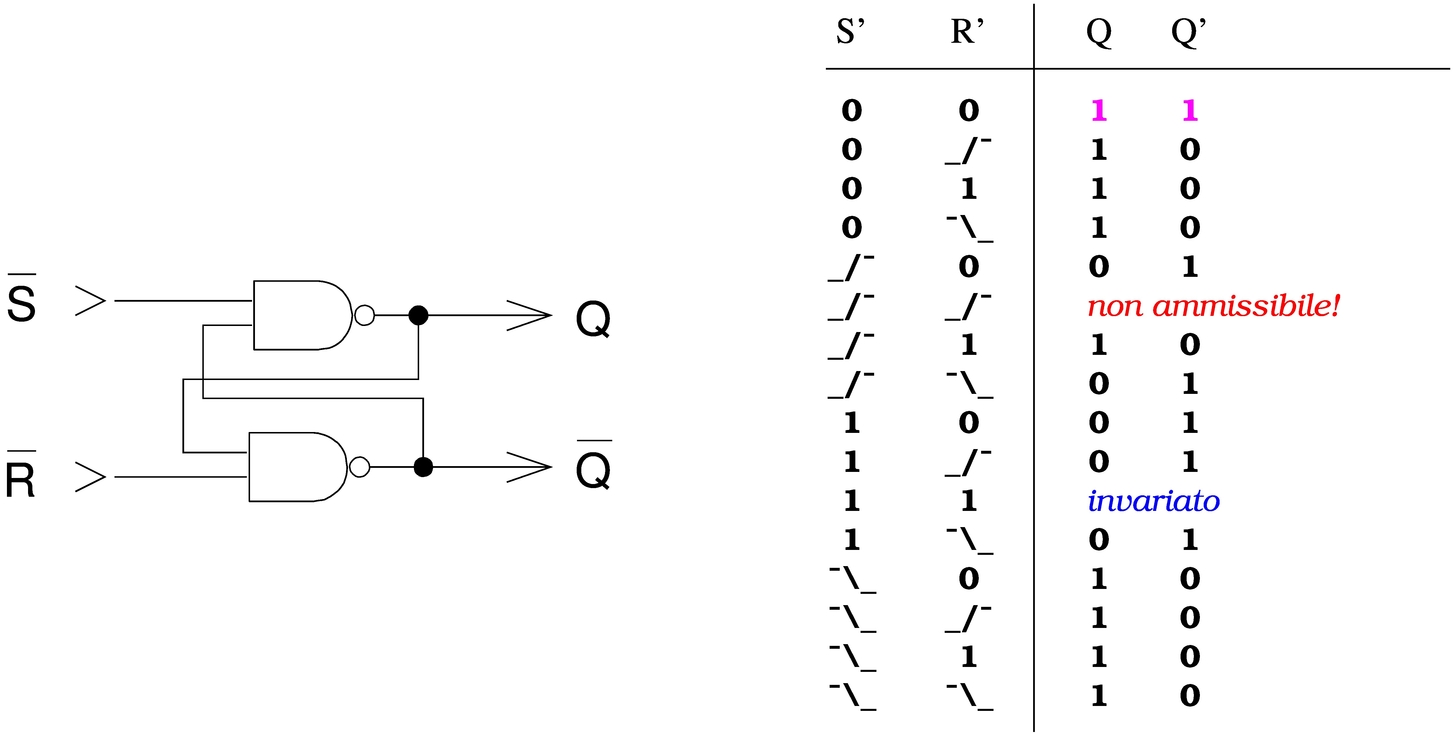

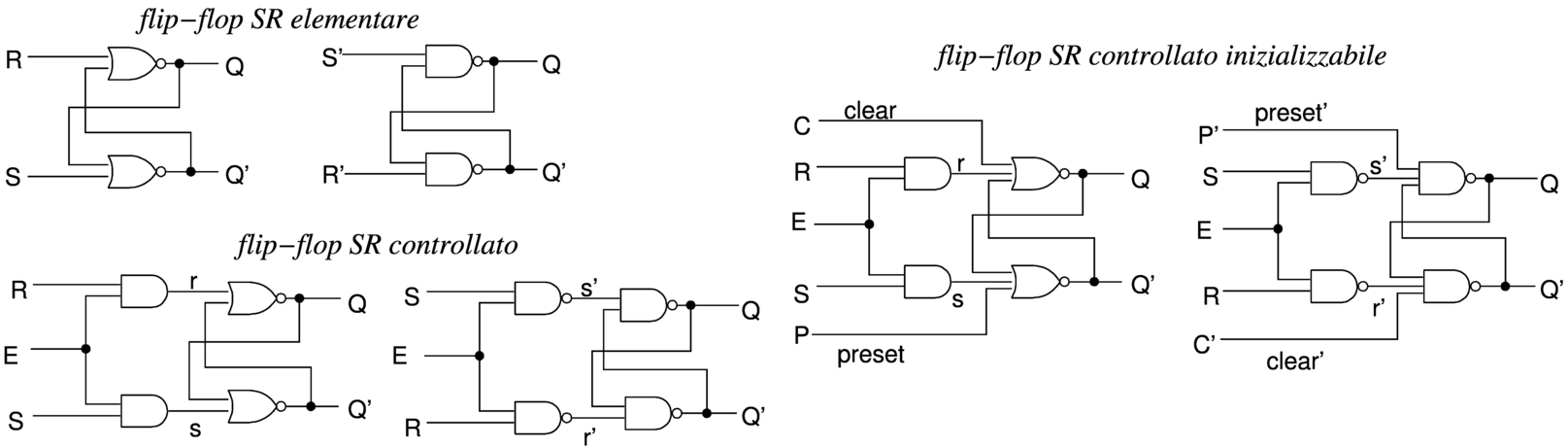

Flip-flop SR elementare

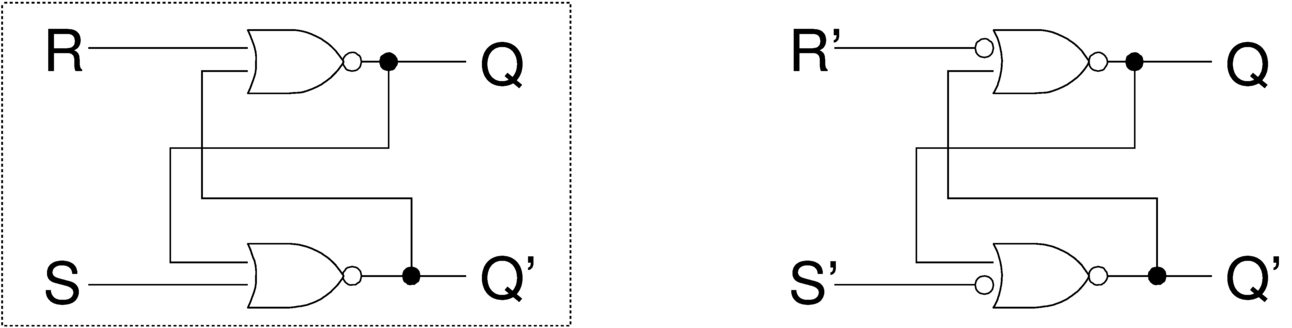

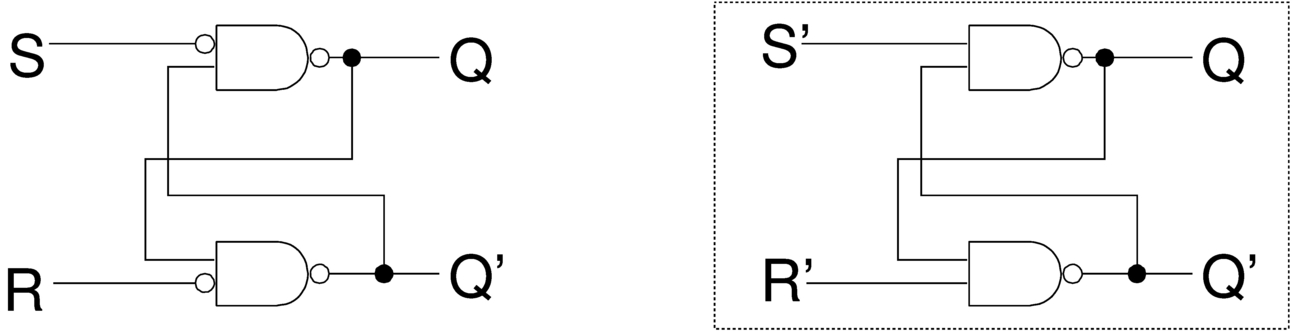

L'esempio più semplice di circuito sequenziale che mantiene la memoria del proprio stato, è quello che si può vedere nelle due figure successive, realizzato rispettivamente con porte NOR e NAND. Nel caso del circuito con porte NOR, si parte da uno stato iniziale in cui l'uscita Q ha un valore indeterminabile (potrebbe essere zero oppure uno, in base a fattori imponderabili), quindi, attivando l'ingresso S (set), anche solo con un breve impulso, l'uscita Q si attiva e rimane attiva fino a quando non riceve un impulso dall'ingresso R (reset); nel caso del circuito con porte NAND, gli ingressi S' e R' funzionano in modo negato.

|

Figura u129.5. Circuito elementare di tipo set-reset con porte NOR.

|

|

Figura u129.6. Circuito elementare di tipo set-reset con porte NAND.

|

Nelle tabelle di verità che appaiono a fianco dei disegni, si può osservare che esiste una situazione inammissibile: nel primo caso quando entrambi gli ingressi passano da uno a zero; nel secondo, quando passano da zero a uno. Se si tentasse di farlo, si metterebbe il circuito in risonanza, come viene spiegato meglio in seguito.

Le ultime due figure apparse rappresentano in realtà i flip-flop SR elementari, i quali però si disegnano solitamente aggiungendo un'uscita ulteriore, Q', che assume un valore inverso rispetto a Q.

|

Figura u129.7. Flip-flop SR elementare, realizzato con porte NOR.

|

|

Figura u129.8. Flip-flop SR elementare, realizzato con porte NAND.

|

|

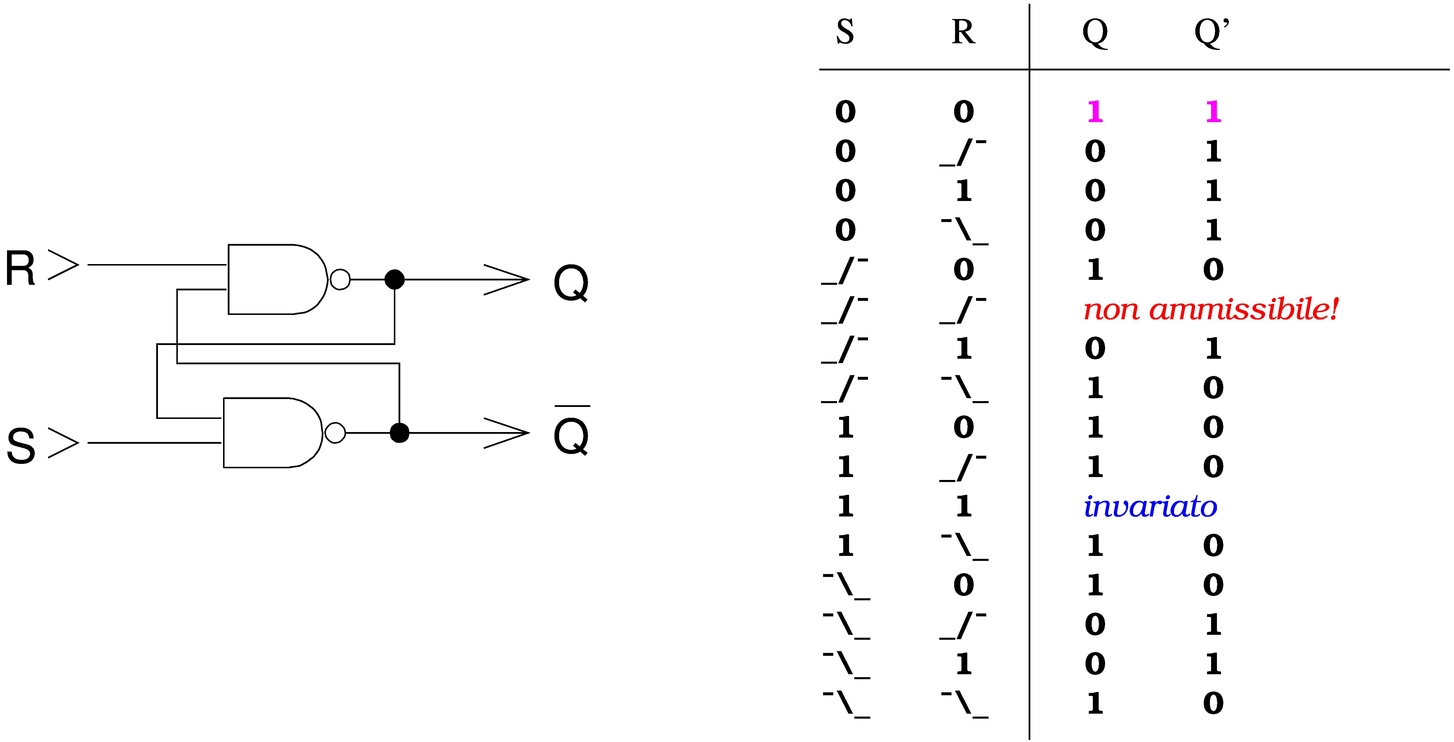

Figura u129.9. Flip-flop SR elementare, realizzato con porte NAND cambiando il significato degli ingressi.

|

Il flip-flop SR elementare realizzato con porte NAND è equivalente a quello realizzato con porte NOR, se al primo si invertono gli ingressi; tuttavia, il flip-flop SR con porte NAND si usa spesso cambiando nome agli ingressi, come avviene nell'ultima figura mostrata, ma in tal caso, il comportamento non risulta uguale a quello fatto con porte NOR, anche se vi si avvicina. Per questo problema, quando si disegna un flip-flop SR elementare come scatola, bisogna chiarire a quale tabella di verità si sta facendo riferimento; tuttavia, l'uso di flip-flop SR elementari è molto limitato, pertanto nel disegno dei circuiti è meglio evitare di rappresentarli come scatole.

|

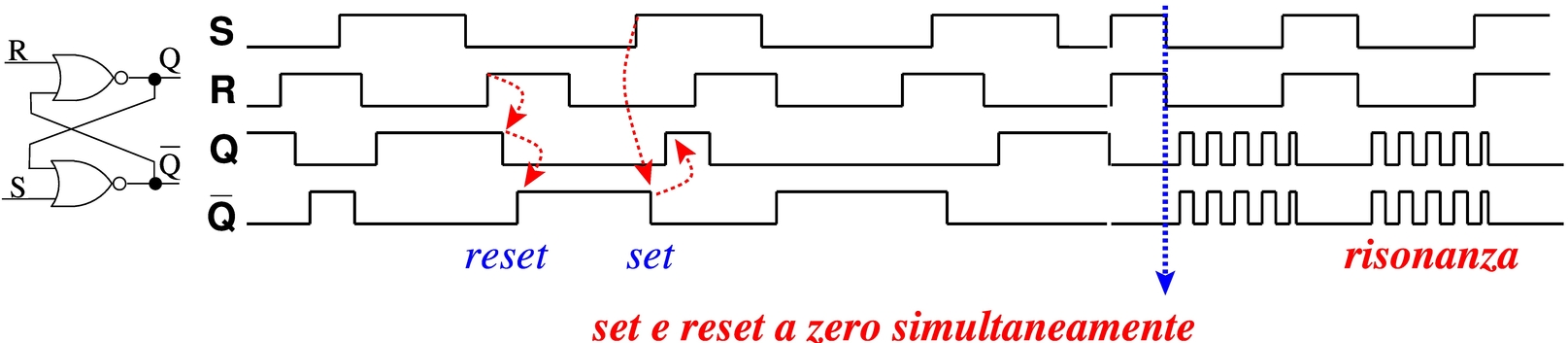

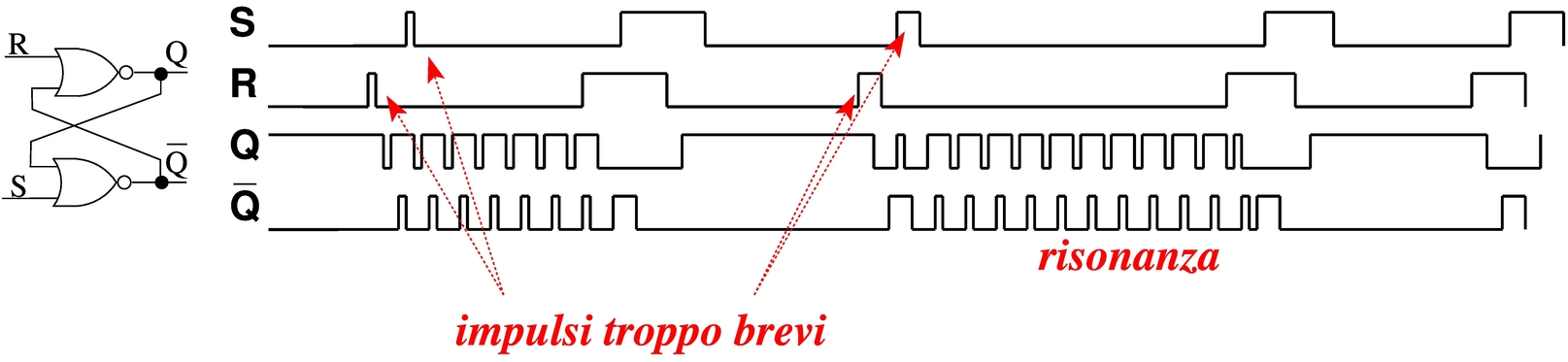

Figura u129.10. Tracciati di un flip-flop SR elementare basato su porte NOR, evidenziando la situazione critica che si crea quando entrambi gli ingressi si trovano attivati assieme e poi si azzerano simultaneamente e quella che si crea quando l'attivazione degli ingressi ha una durata troppo breve.

|

La figura mostra il tracciato dei valori delle entrate e quello delle uscite di un flip-flop SR elementare e con questo si può vedere l'effetto del ritardo di propagazione, ma soprattutto ciò che accade quando gli ingressi da attivi passano simultaneamente a zero: a causa del ritardo di propagazione, le due uscite rimangono per un po' a zero, poi, però, trovando gli ingressi a zero, si attivano simultaneamente e innescano un circolo vizioso. Pertanto, nel flip-flop SR elementare, è necessario evitare la condizione inammissibile già mostrata nelle tabelle di verità. Ma anche un impulso troppo breve in uno degli ingressi può procurare un effetto di risonanza: in generale, la durata minima di un impulso negli ingressi deve essere tale da consentire al flip-flop di cambiare stato, quando tale impulso lo prevederebbe.

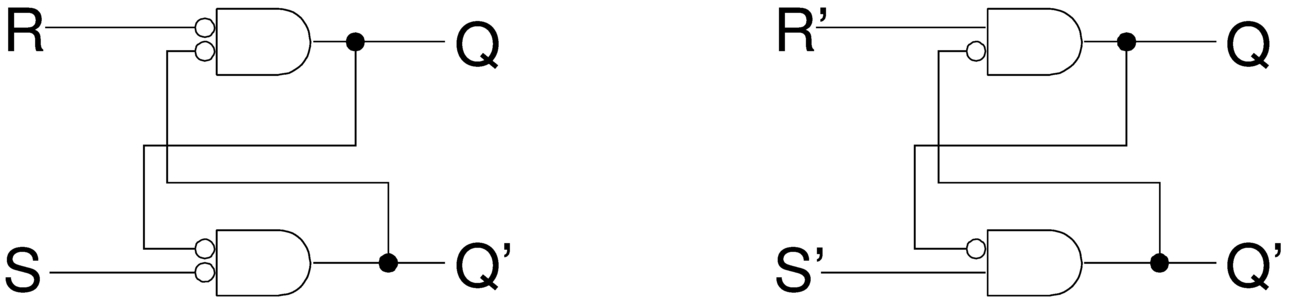

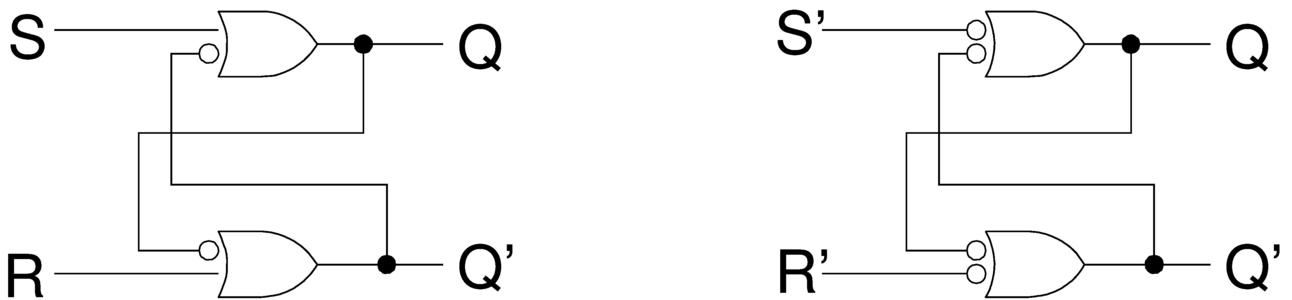

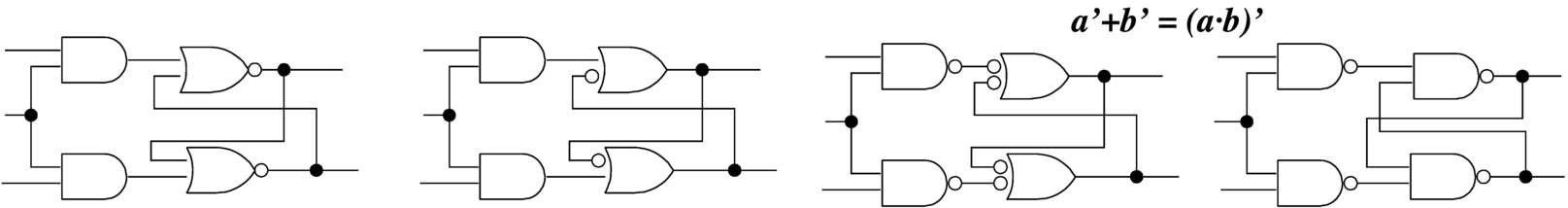

Nonostante la sua limitazione, a proposito della presenza di condizioni di ingresso inammissibili, il flip-flop SR elementare costituisce la base per tutti gli altri tipi di flip-flop. Per tale motivo è importante conoscere in quali altre forme può essere realizzato, come dimostrato nella figura successiva.

|

Figura u129.11. Flip-flop SR elementare in varie forme alternative, nelle quali occorre fare attenzione all'ordine degli ingressi. Nella colonna di sinistra si mostrano nella versione a ingressi positivi, mentre in quella destra appaiono nella versione a ingressi invertiti. Nei due gruppi sono evidenziati i due tipi più comuni: NOR e NAND.

|

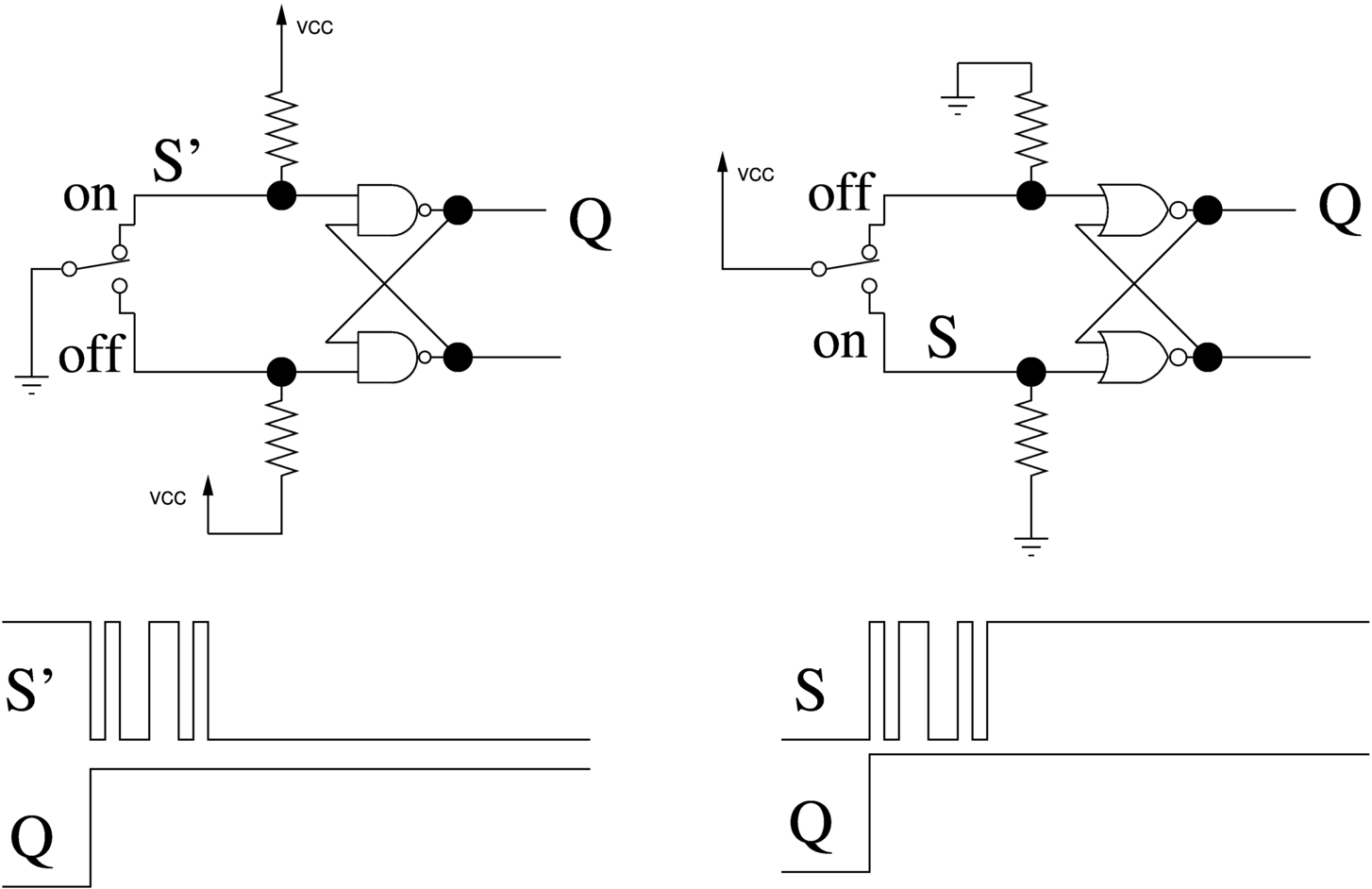

Interruttori senza rimbalzi

Nella realizzazione pratica di circuiti logici (elettronici) si ha spesso la necessità di utilizzare degli interruttori o pulsanti. Ma nella vita reale, tali componenti hanno il problema dei rimbalzi, nel senso che l'apertura o la chiusura di un interruttore comporta la creazione di impulsi indesiderabili. Per impedire che tali impulsi arrivino a un circuito, si utilizzano i flip-flop SR elementari, per esempio nella modalità che si può vedere nella figura successiva.

|

Figura u129.12. Utilizzo di un flip-flop SR elementare per filtrare i rimbalzi di un interruttore.

|

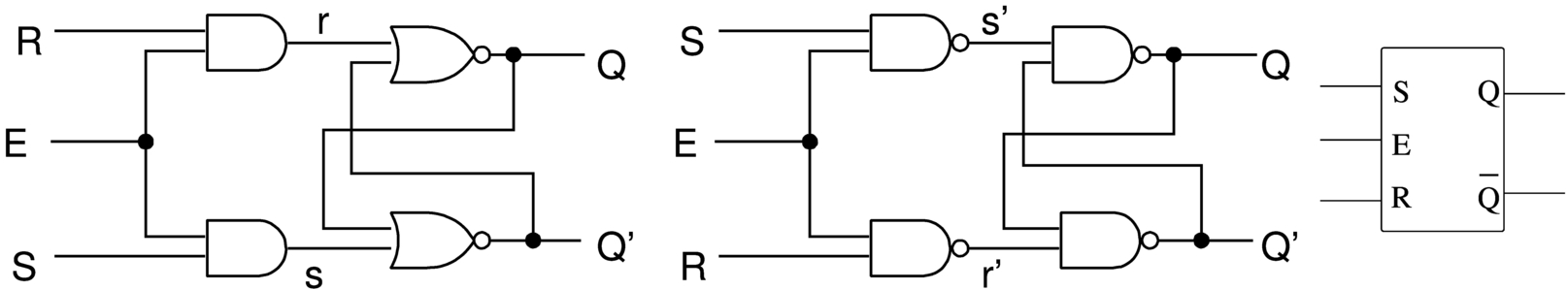

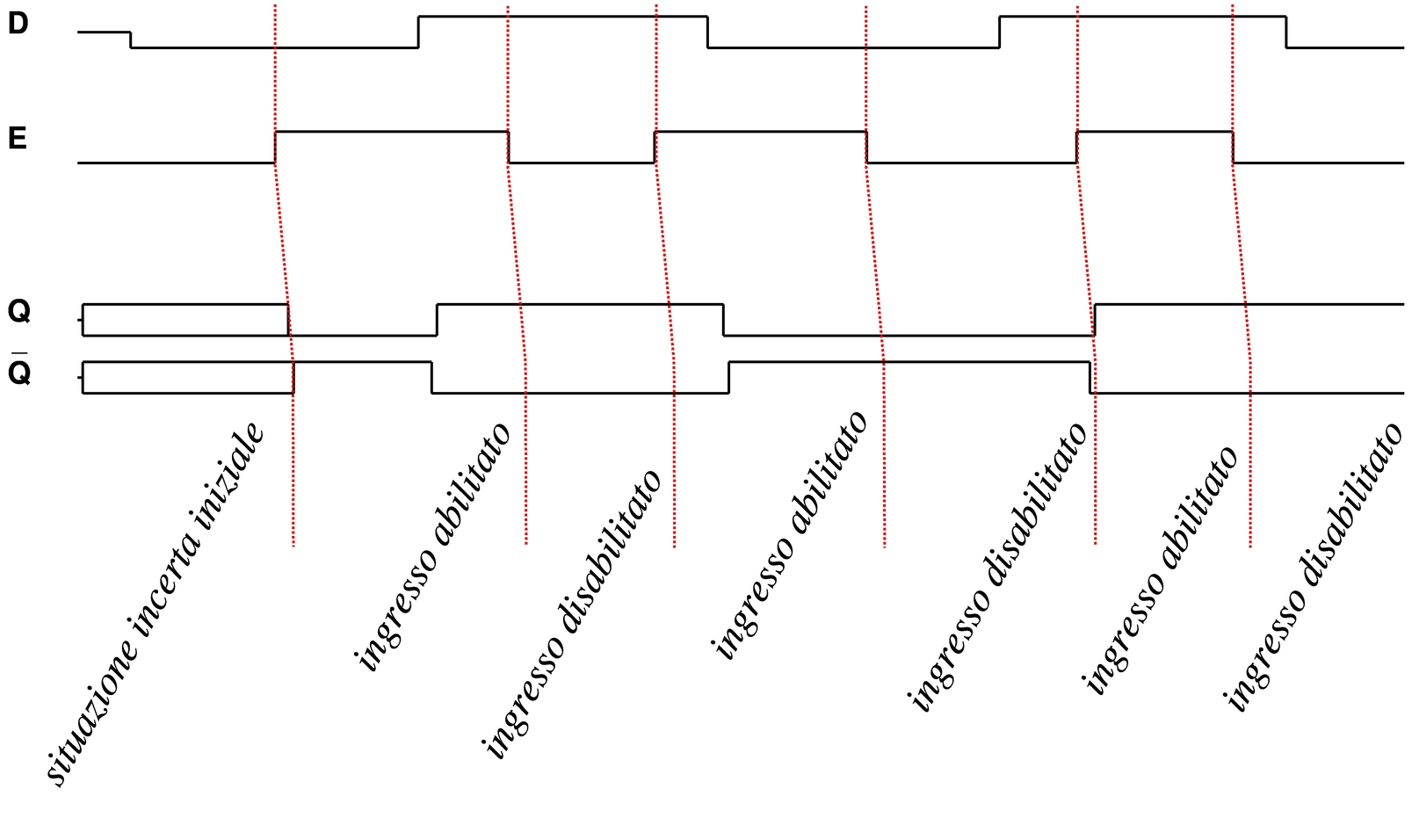

Flip-flop SR con gli ingressi controllati

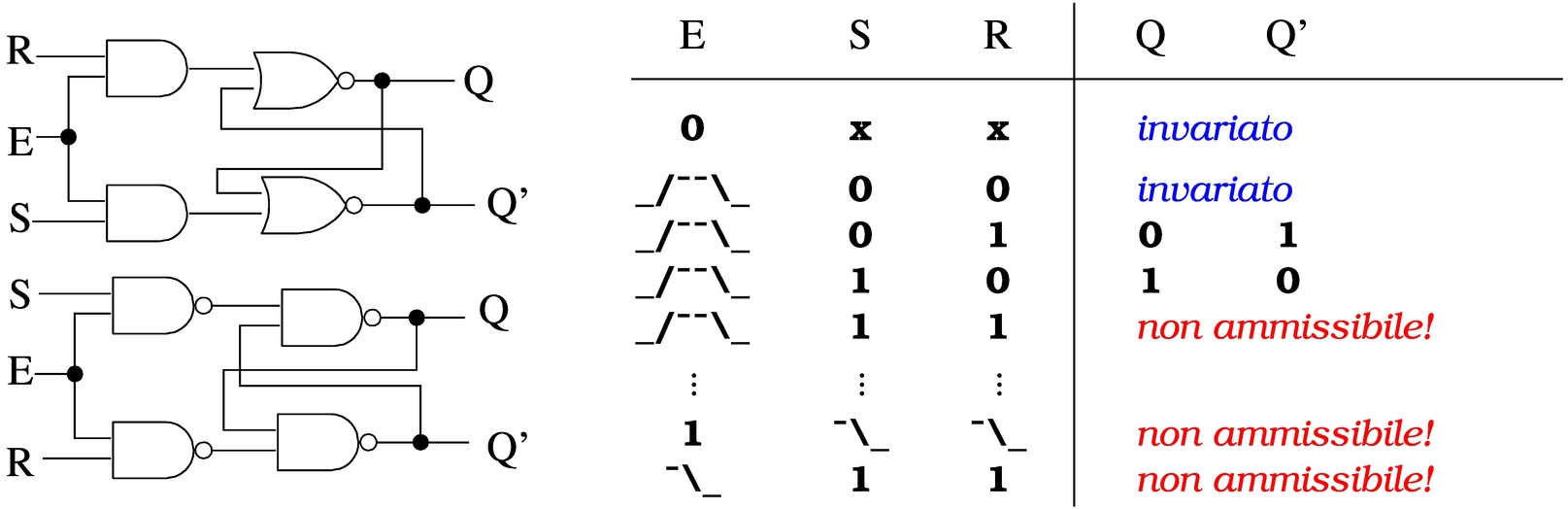

Il flip-flop SR elementare può essere esteso aggiungendo un controllo di abilitazione degli ingressi, con due porte AND o NAND, a seconda del tipo: in pratica, così facendo, quando l'ingresso di abilitazione è attivo, il flip-flop SR funziona normalmente, mentre diversamente è come se entrambi gli ingressi si trovassero a zero.

|

Figura u129.13. Flip-flop SR controllato: quando l'ingresso E (enable) è attivo, funziona come un flip-flop SR elementare; se invece l'ingresso E non è attivo, è come se gli ingressi S e R fossero disattivati a loro volta. Il circuito appare nelle due versioni più comuni, assieme alla simbologia usata normalmente per rappresentare questo tipo di flip-flop.

|

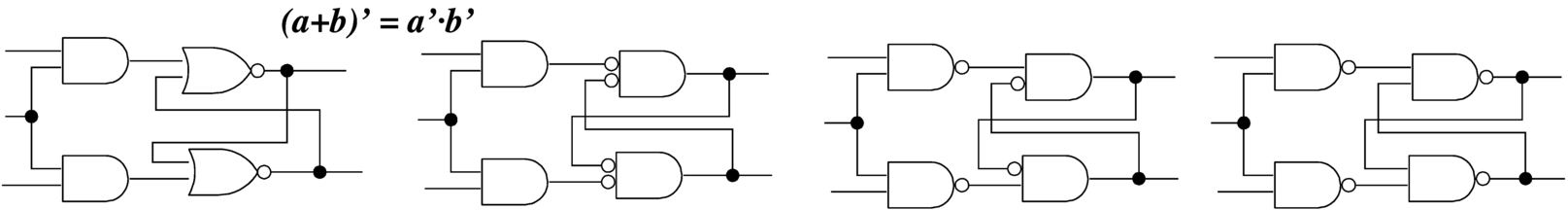

I due schemi che appaiono nella figura sono equivalenti e lo si dimostra facilmente, con l'aiuto dei teoremi di De Morgan, come si vede nei disegni seguenti.

|

Figura u129.14. Dimostrazione dell'equivalenza dei due modi di rappresentare i flip-flop SR controllati.

|

Nel flip-flop SR controllato rimangono i problemi di innesco della risonanza già descritti: in pratica, è indispensabile che l'ingresso di abilitazione (E) sia attivo solo quando gli ingressi S e R si trovano in una condizione valida, ma rispetto al flip-flop SR elementare, non è nemmeno ammesso che gli ingressi siano attivi simultaneamente, perché all'abbassarsi della linea di abilitazione si creerebbe inevitabilmente l'innesco.

|

Figura u129.15. Tabella di verità per il flip-flop SR controllato, limitatamente ai casi più significativi.

|

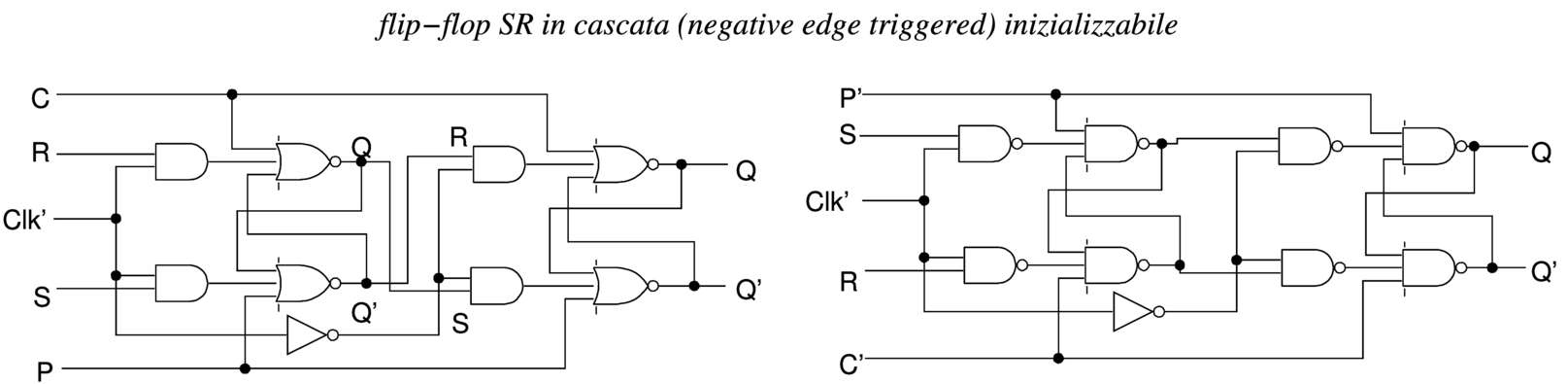

Quando si mette in funzione un flip-flop, lo stato delle uscite è indeterminabile. Per poter inizializzare il flip-flop SR controllato, è necessario estendere gli ingressi delle porte del flip-flop SR elementare, come mostrato nella figura successiva. Va osservato che a seconda di come si realizza il flip-flop SR, può darsi che per inizializzare il flip-flop possa richiedersi un valore a uno o a zero.

|

Figura u129.16. Flip-flop SR controllato, con ingressi di inizializzazione: quando l'ingresso P (preset) è attivo, si forza l'attivazione dell'uscita Q; quando l'ingresso C (clear) è attivo, si forza l'attivazione dell'uscita Q'. Il circuito viene mostrato nelle due varianti realizzative comuni, assieme alla rappresentazione simbolica complessiva. Va osservato che nella seconda modalità, gli ingressi P e C sono invertiti (negati).

|

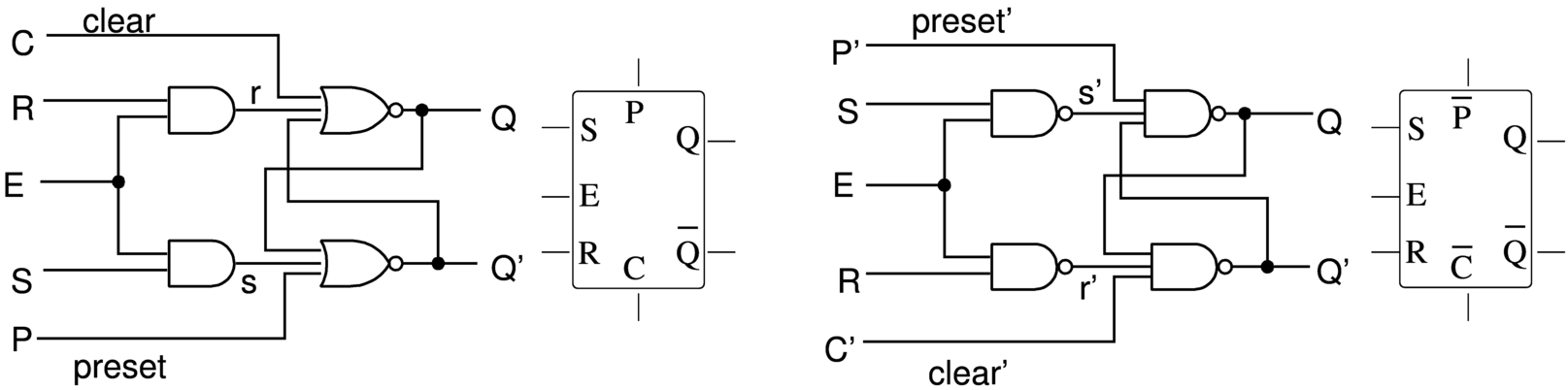

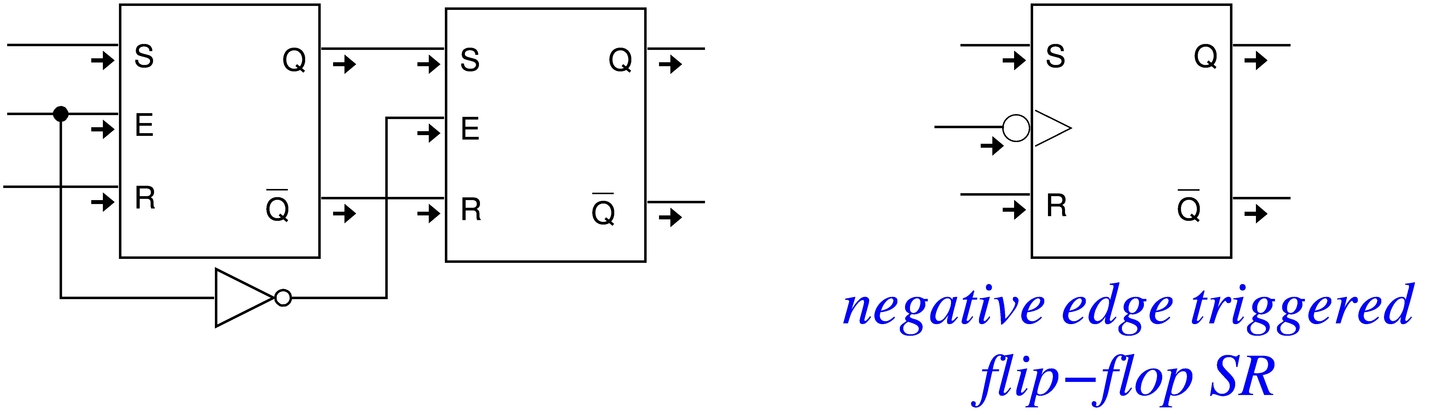

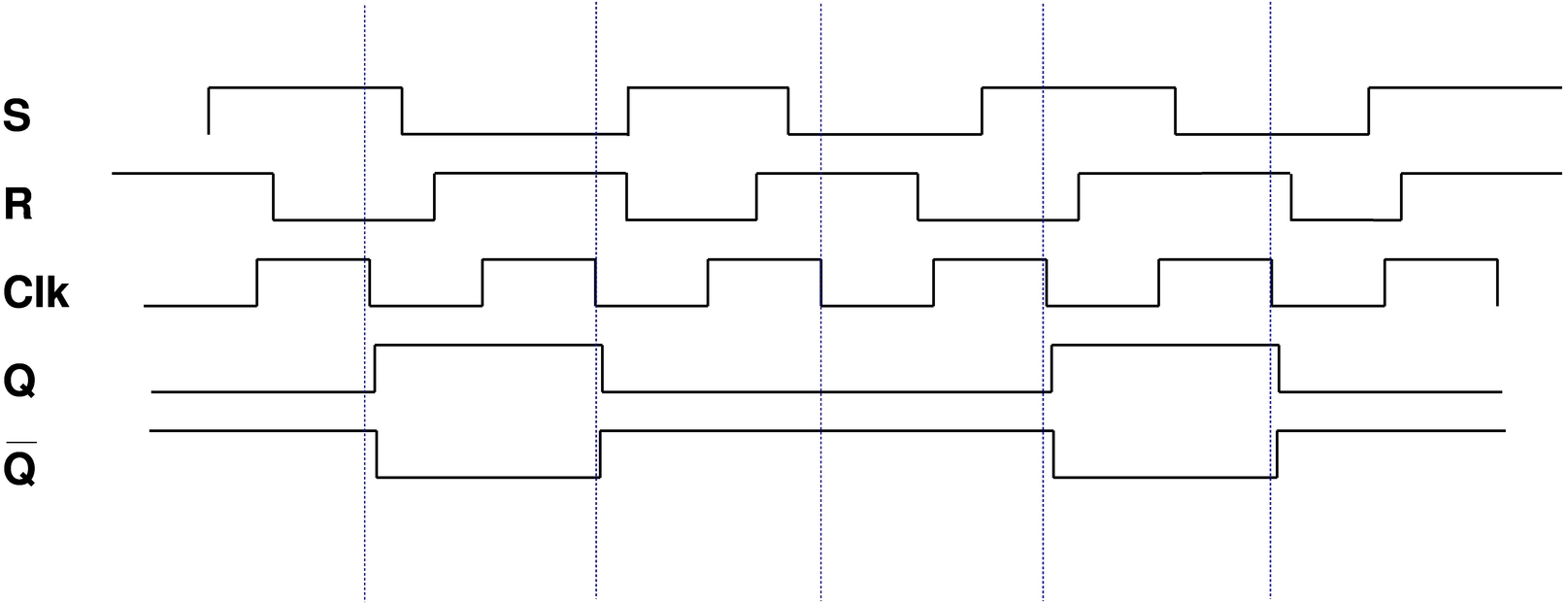

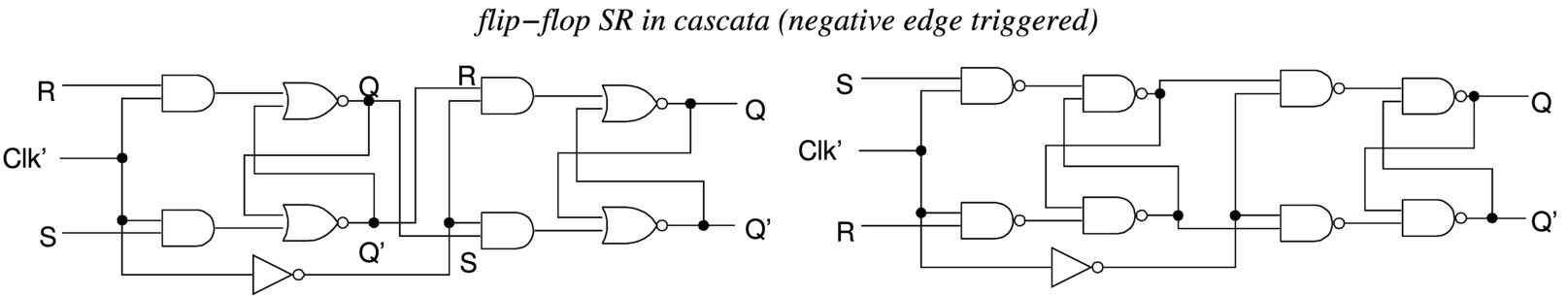

Flip-flop SR sincrono «edge triggered»

Nel flip-flop controllato attraverso l'ingresso di abilitazione (o di clock), quando tale ingresso di abilitazione è attivo, i valori degli altri ingressi possono cambiare e il loro cambiamento può trasmettersi regolarmente nel flip-flop modificando eventualmente lo stato delle uscite. Per fare in modo che il controllo di abilitazione fotografi la situazione degli ingressi, occorre che sia pilotato da un impulso abbastanza breve, ma non troppo, tale per cui in quel lasso di tempo i valori degli ingressi non possano cambiare. Per ovviare a questo problema, si possono mettere due flip-flop SR controllati in cascata (master-slave), dove il secondo riceve il segnale di abilitazione invertito rispetto al primo; tuttavia, in tal caso l'aggiornamento del flip-flop complessivo si ottiene nel momento in cui il segnale di abilitazione si disattiva, ovvero in corrispondenza del margine negativo (negative edge).

|

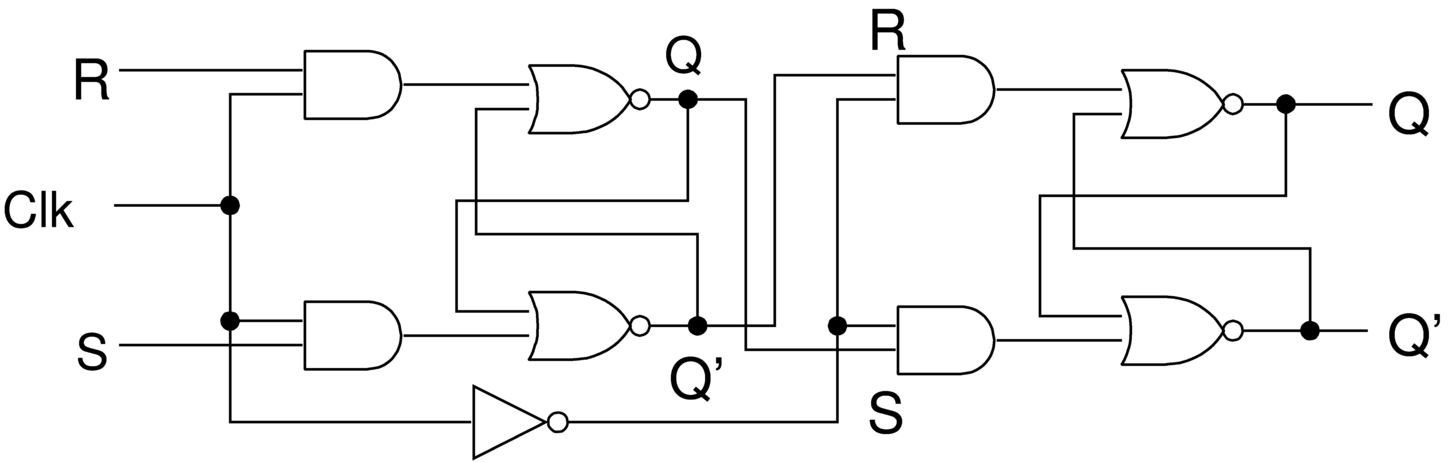

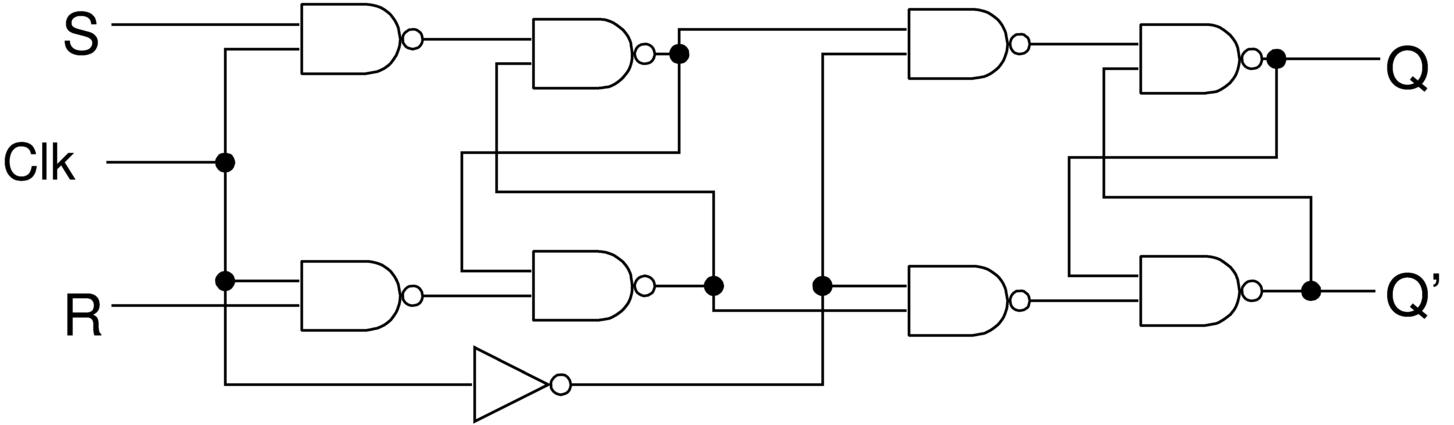

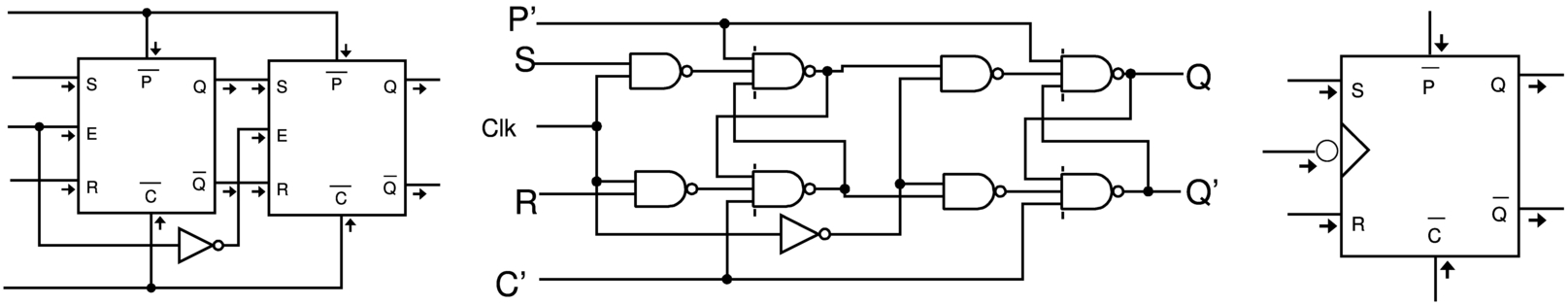

Figura u129.17. Flip-flop SR sincrono a margine negativo: quando il segnale di abilitazione passa da attivo a zero, il flip-flop si aggiorna. Il circuito viene mostrato a blocchi e nelle due varianti realizzative comuni, assieme alla rappresentazione simbolica complessiva, dove va osservato che l'ingresso di abilitazione viene annotato con un triangolo, per sottolineare il fatto che il segnale viene recepito in corrispondenza della sua variazione.

|

|

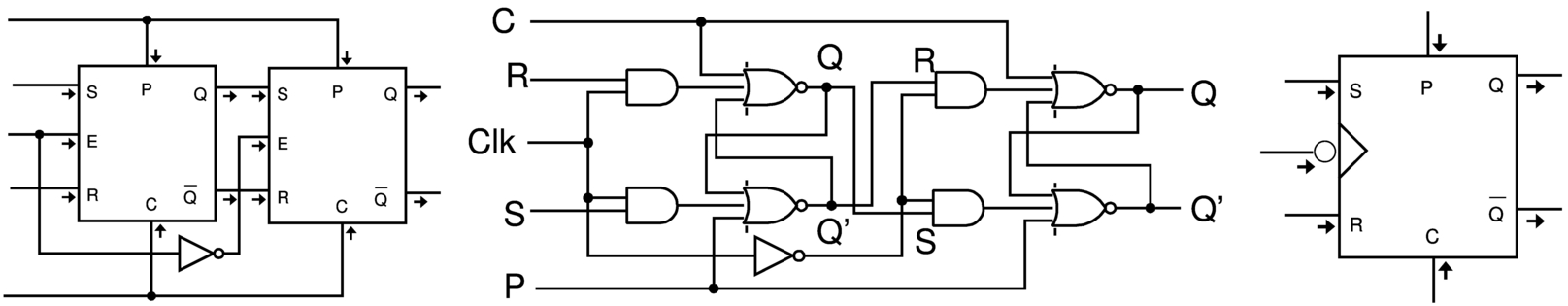

Figura u129.18. Completamento del flip-flop SR sincrono a margine negativo, con gli ingressi di inizializzazione.

|

|

Figura u129.19. Riassunto delle varie tipologie di flip-flop SR.

|

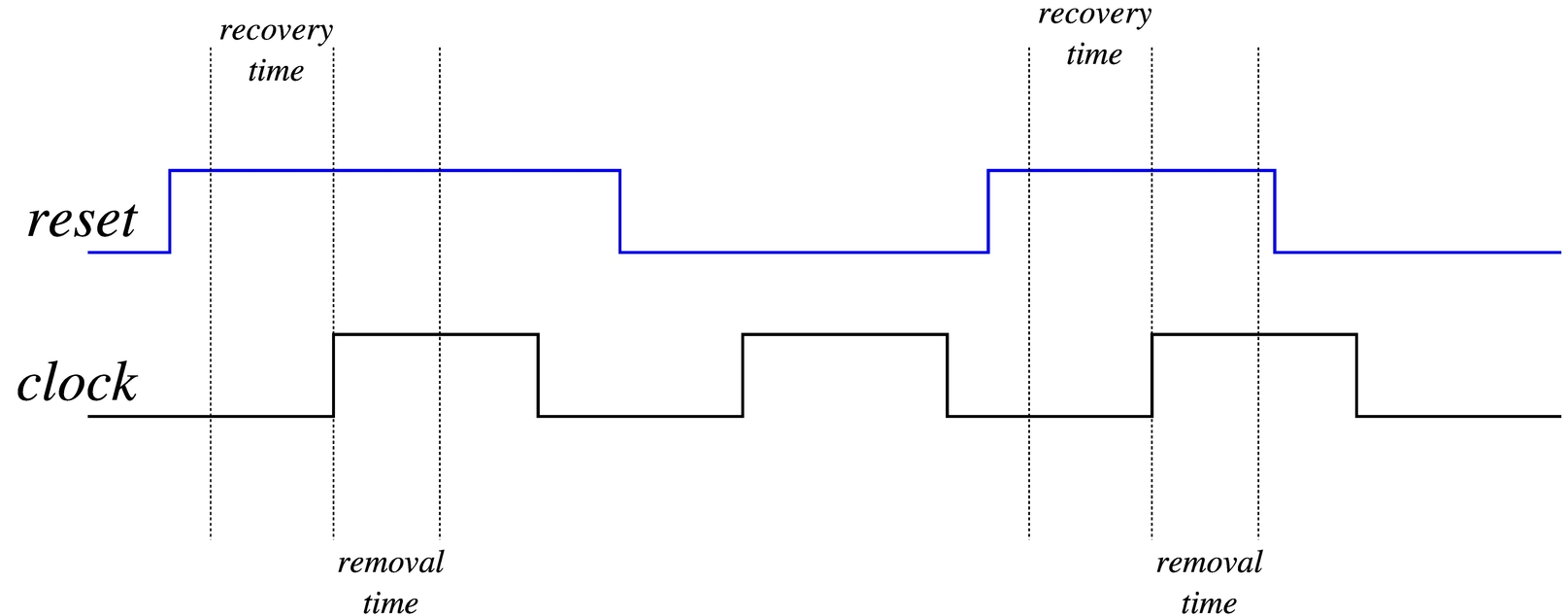

Tempo: setup/hold e recovery/removal

Si distinguono due intervalli di tempo significativi per i componenti sincroni, ovvero quelli che hanno un ingresso dati controllato da un ingresso di abilitazione o di clock. Si tratta del tempo di attivazione, setup time, noto con la sigla tsu, e del tempo di mantenimento, hold time, noto con la sigla th.

|

Figura u129.20. Esempio di situazioni corrette e non corrette, relativamente ai vincoli del tempo di attivazione (tsu) e del tempo di mantenimento (th).

|

In contesti diversi, quando si vuole sottolineare il fatto che il dato in ingresso è un'informazione asincrona, si usa un'altra terminologia: recovery time e removal time.

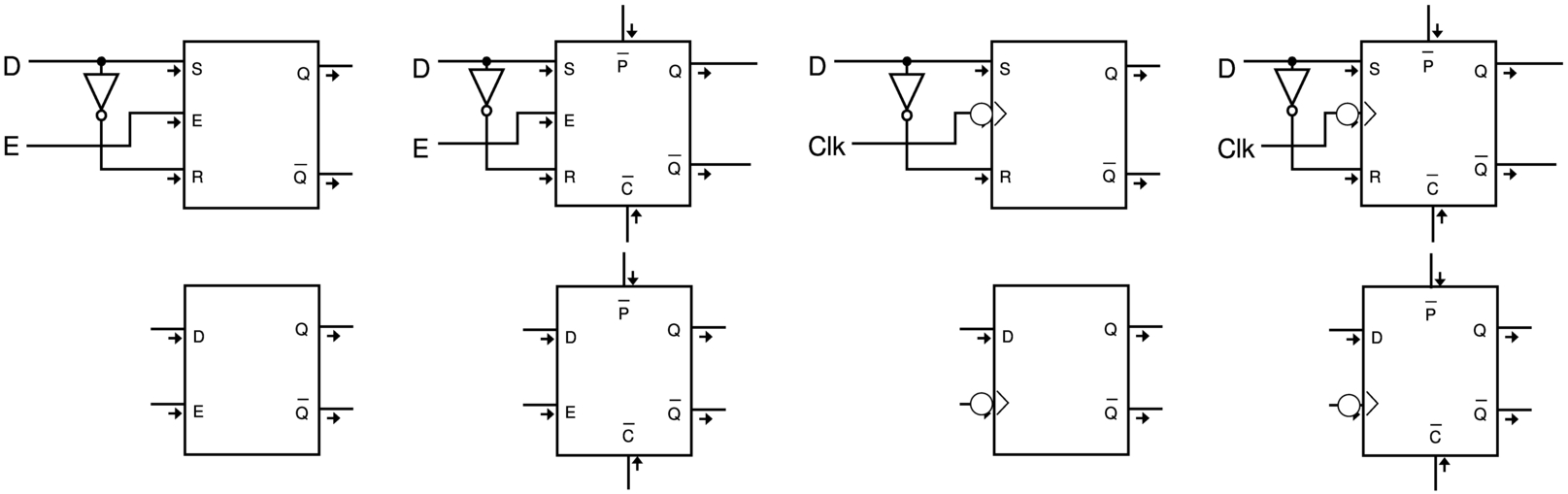

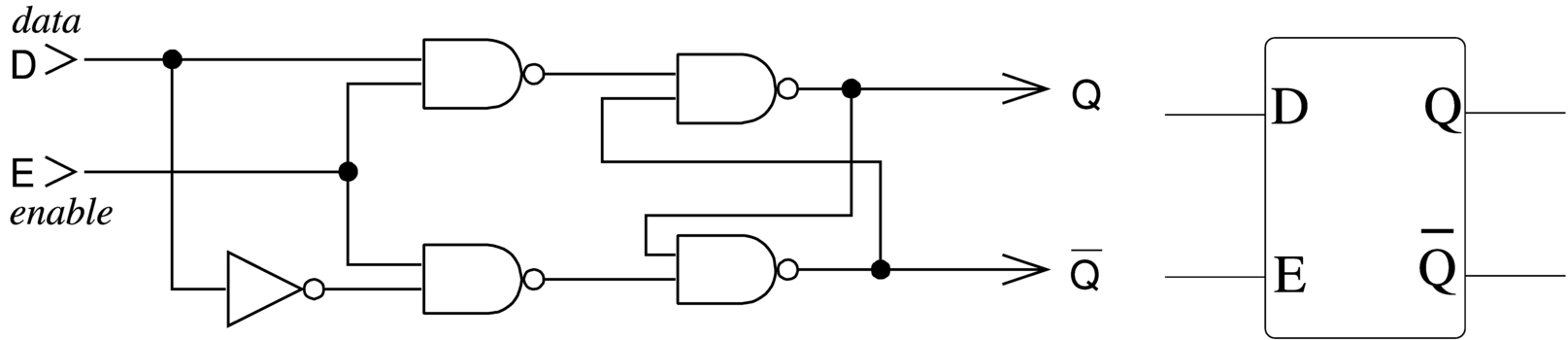

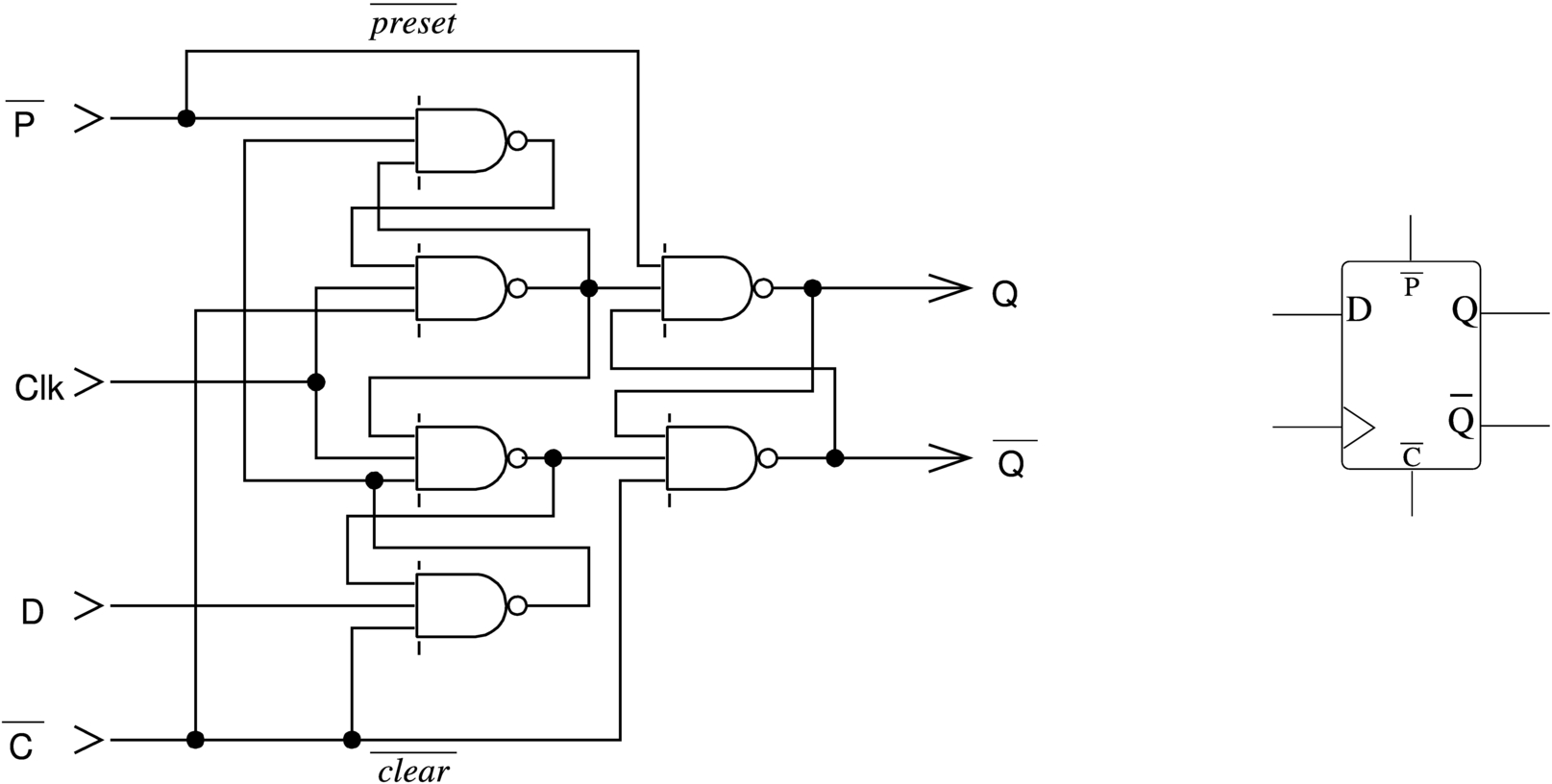

Flip-flop D

Il flip-flop D (data) si ottiene da un flip-flop SR, collegando assieme i due ingressi, invertendo però l'ingresso R. In pratica, il flip-flop D è utile solo quando c'è almeno il controllo di abilitazione degli ingressi.

|

Figura u129.22. Flip-flop D ottenuto dal flip-flop SR, nelle varie tipologie ammissibili, a confronto con i simboli corrispondenti. Gli ingressi di inizializzazione e di clock sono stati mostrati solo nella versione negata, essendo la più comune.

|

Sul flip-flop D valgono le stesse considerazioni fatte sul flip-flop SR, per quanto riguarda il tempo di attivazione e il tempo di mantenimento dell'impulso di abilitazione. Rispetto al flip-flop SR, essendoci un solo ingresso dati, non ci sono combinazioni inammissibili.

|

Figura u129.23. Flip-flop D con ingresso di abilitazione semplice, realizzato utilizzando porte NAND. Quando l'ingresso E è attivo, il circuito recepisce il dato dall'ingresso D e lo riproduce attraverso l'uscita Q (invertendolo nell'uscita Q').

|

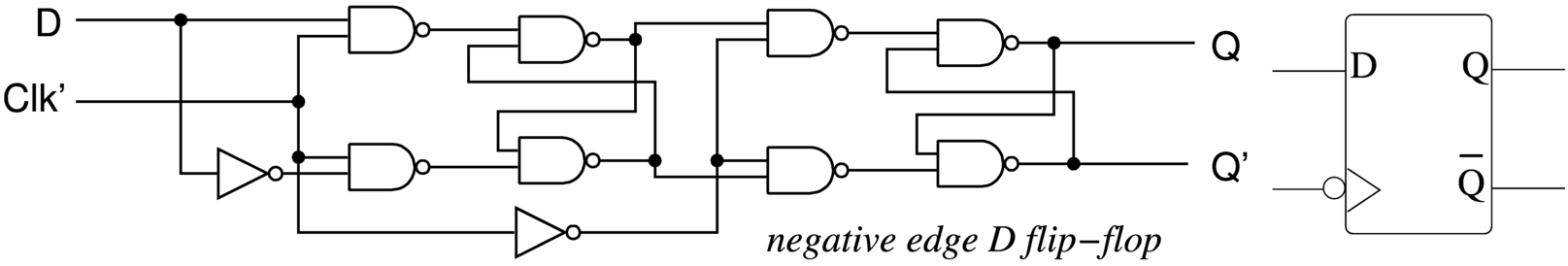

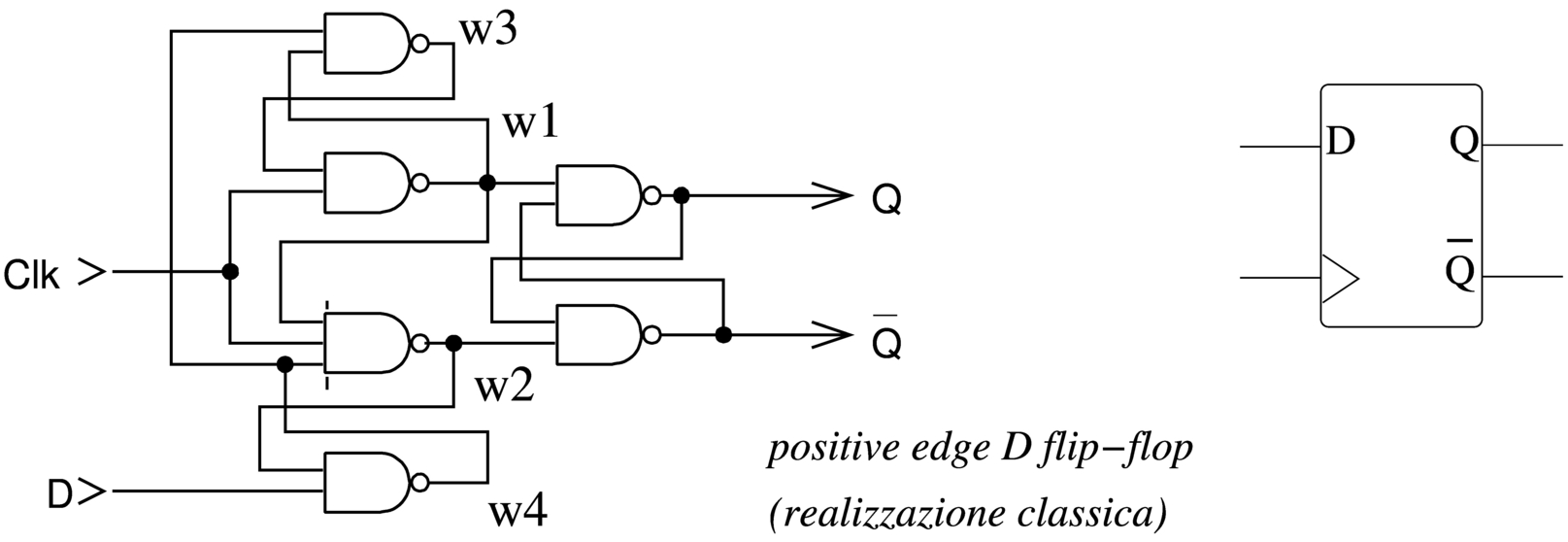

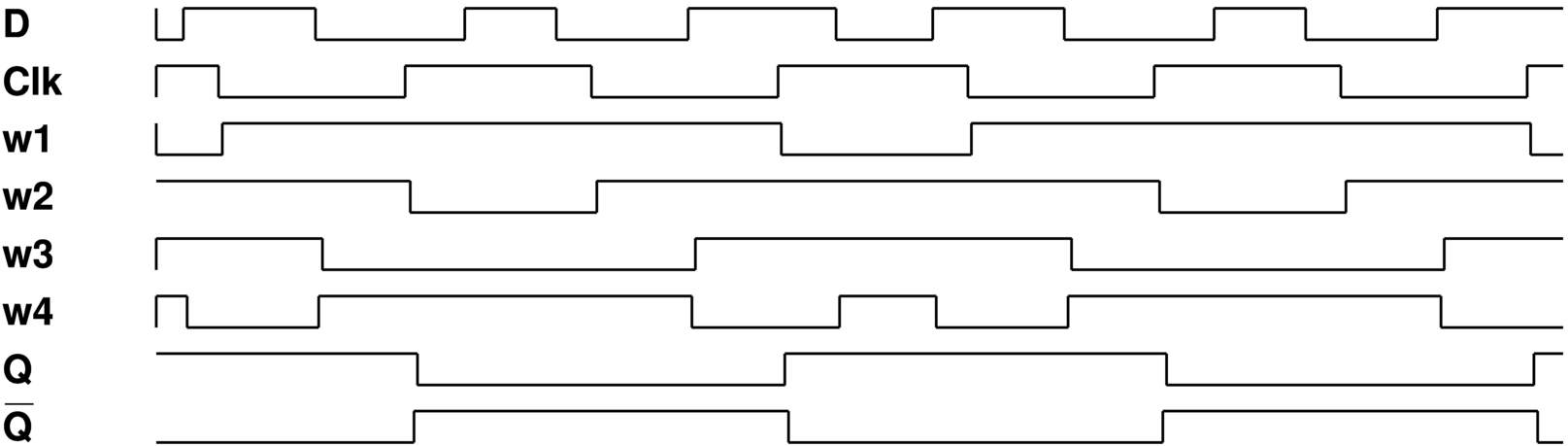

Il flip-flop D, attivato dalla variazione del segnale di clock, può essere realizzato in cascata, come già visto per il flip-flop RS, Tuttavia esiste un circuito alternativo più efficiente: in tal caso, il margine di attivazione del flip-flop D, diventa quello positivo.

|

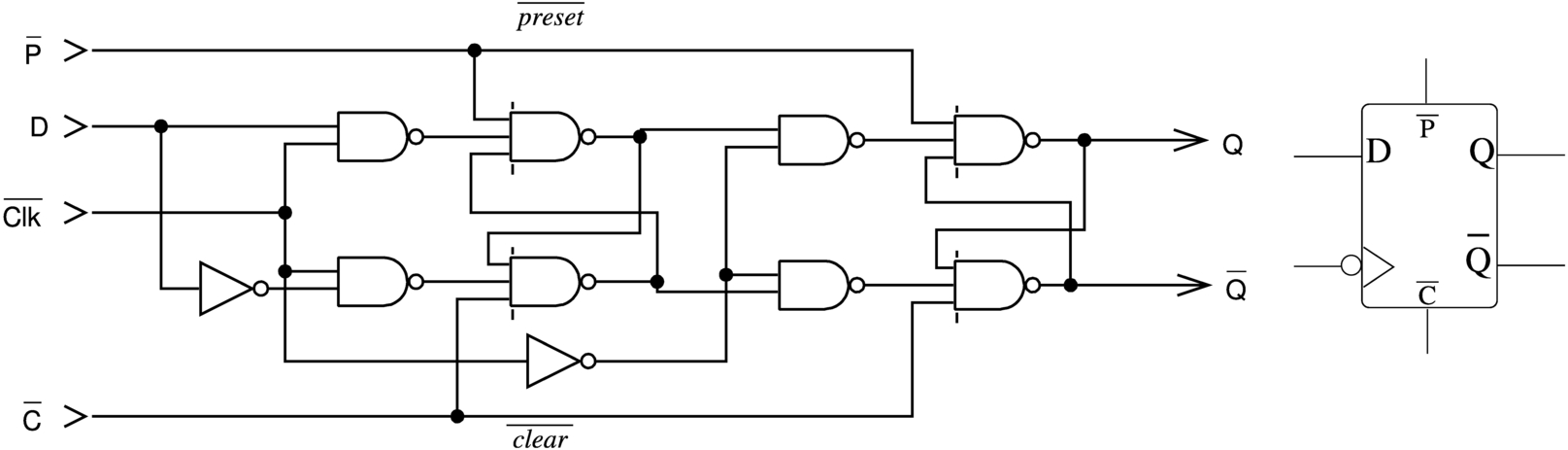

Figura u129.24. Flip-flop D in cascata e nella sua realizzazione classica. Il tracciato riguarda la seconda versione che risulta funzionare a margine positivo.

|

|

Figura u129.25. Flip-flop D in cascata e nella sua realizzazione classica, con gli ingressi di inizializzazione.

|

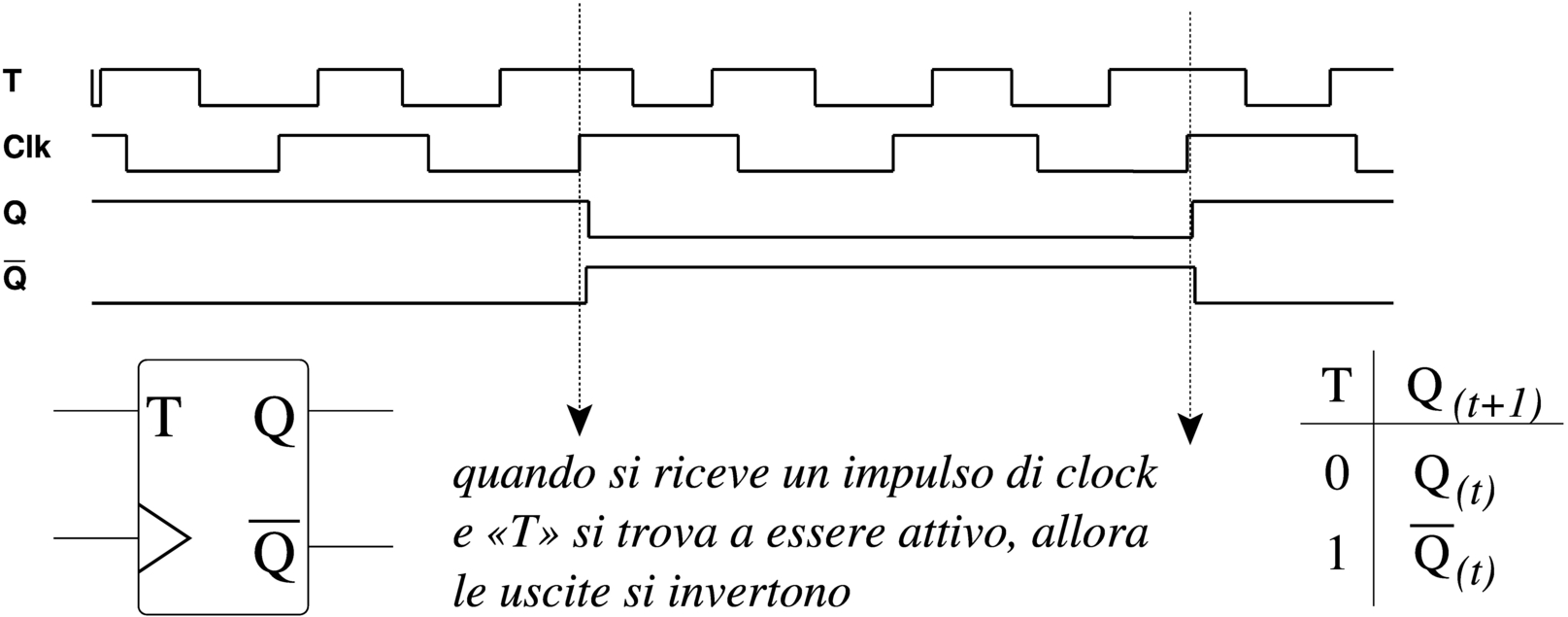

Flip-flop T

Estendendo leggermente un flip-flop D a margine positivo, è possibile ottenere un flip-flop T (toggle), il quale ha lo scopo di invertire il valore delle uscite quando l'ingresso T si attiva per la presenza di un impulso di clock. Nella tabella della verità si usa la notazione Q(t) per indicare il valore dell'uscita Q nel momento t e la notazione Q(t+1) per indicare il valore dell'uscita Q nel momento successivo t+1, corrispondente all'impulso di clock successivo.

|

Figura u129.26. Tracciato, simbolo del flip-flop T e tabella della verità.

|

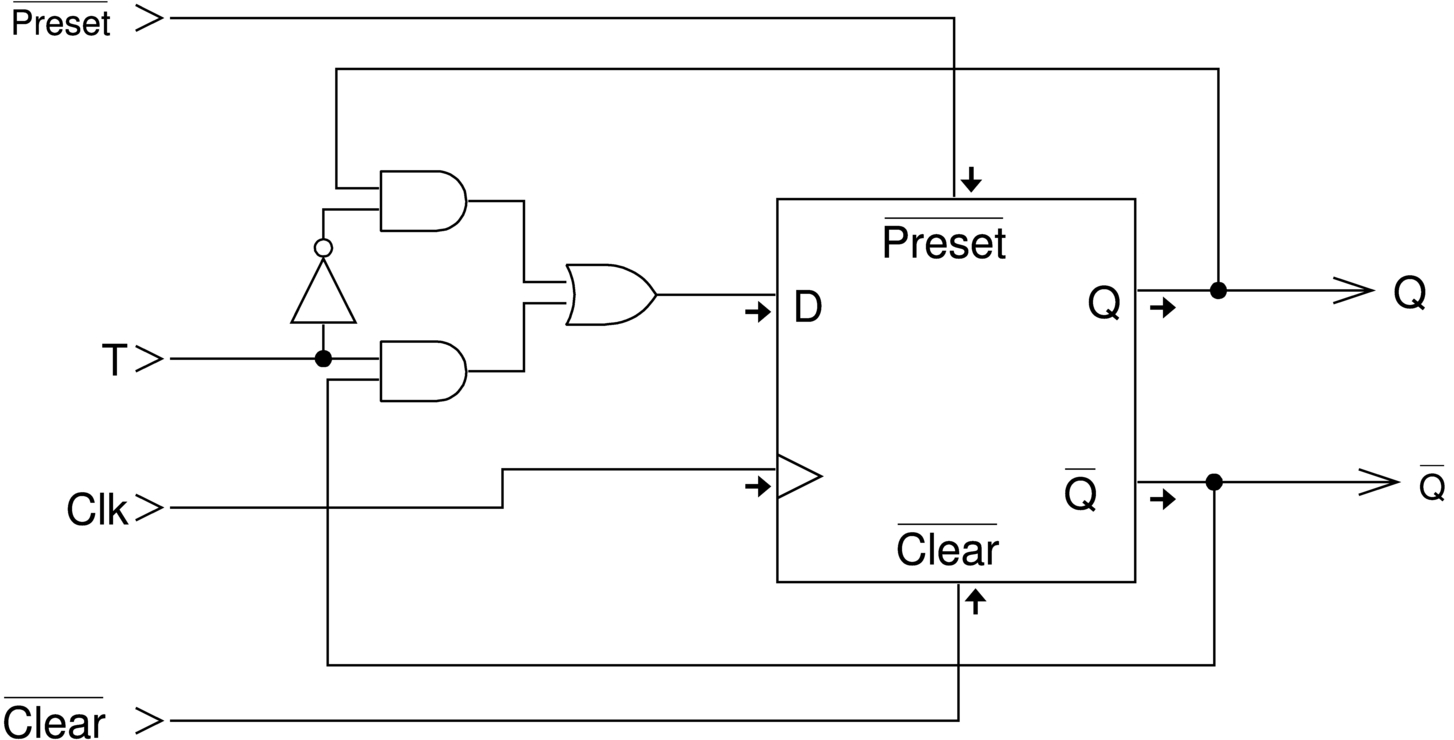

Per realizzare il flip-flop T è necessario tenere in considerazione il fatto che inizialmente non si conosce lo stato delle uscite, quindi è importante poter azzerare il flip-flop all'avvio. Dal momento che si tratta di estendere il flip-flop D, nella figura successiva si parte da quello che dispone degli ingressi di azzeramento e di impostazione.

|

Figura u129.27. Realizzazione del flip-flop T, partendo da un flip-flop D, munito di ingressi di azzeramento e di impostazione. Questa realizzazione è da preferire rispetto a quella della figura successiva.

|

La figura successiva mostra una realizzazione diversa del flip-flop T che in sostanza deriva da un flip-flop JK descritto nel libro Digital Computer Electronics di Malvino e Brown, nel capitolo dedicato ai flip-flop. Tuttavia, attraverso l'uso di un simulatore, si determina che se l'ingresso T riceve un impulso che termina prima che ci sia la variazione negativa del clock, si ottiene ugualmente lo scambio dei valori nelle uscite, mentre ciò non dovrebbe avvenire secondo lo schema di funzionamento previsto per un flip-flop T.

|

Figura u129.28. Realizzazione del flip-flop T, modificando un flip-flop SR in cascata, fatto a sua volta con porte NAND. In tal caso, lo scambio dei valori di uscita avviene in corrispondenza della variazione negativa dell'impulso di clock (negative edge triggered), ma bisogna fare attenzione all'ingresso T, la cui attivazione viene recepita anche se si azzera prima della variazione negativa del clock.

|

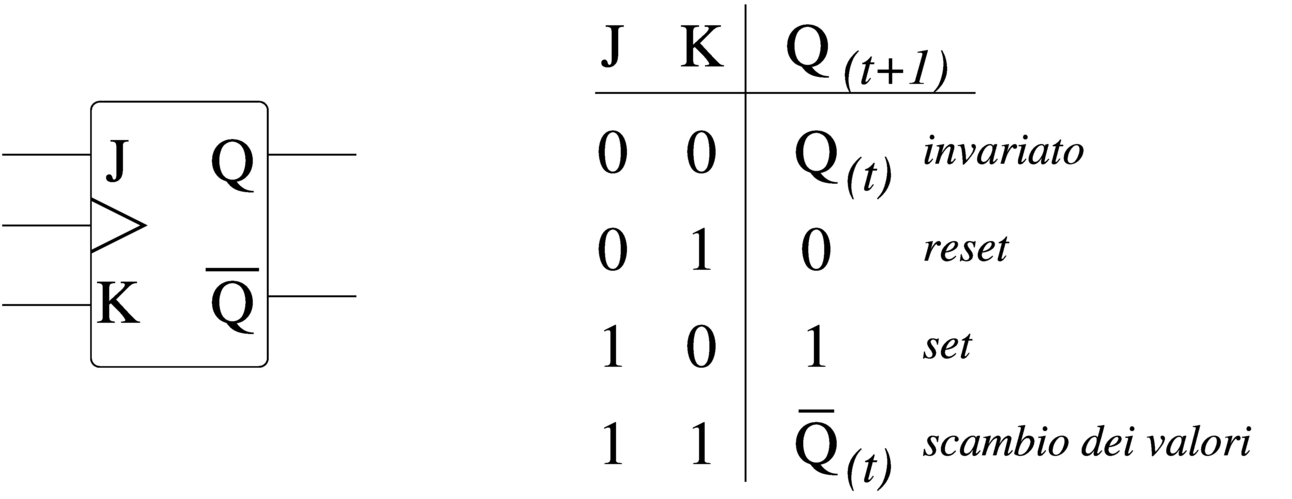

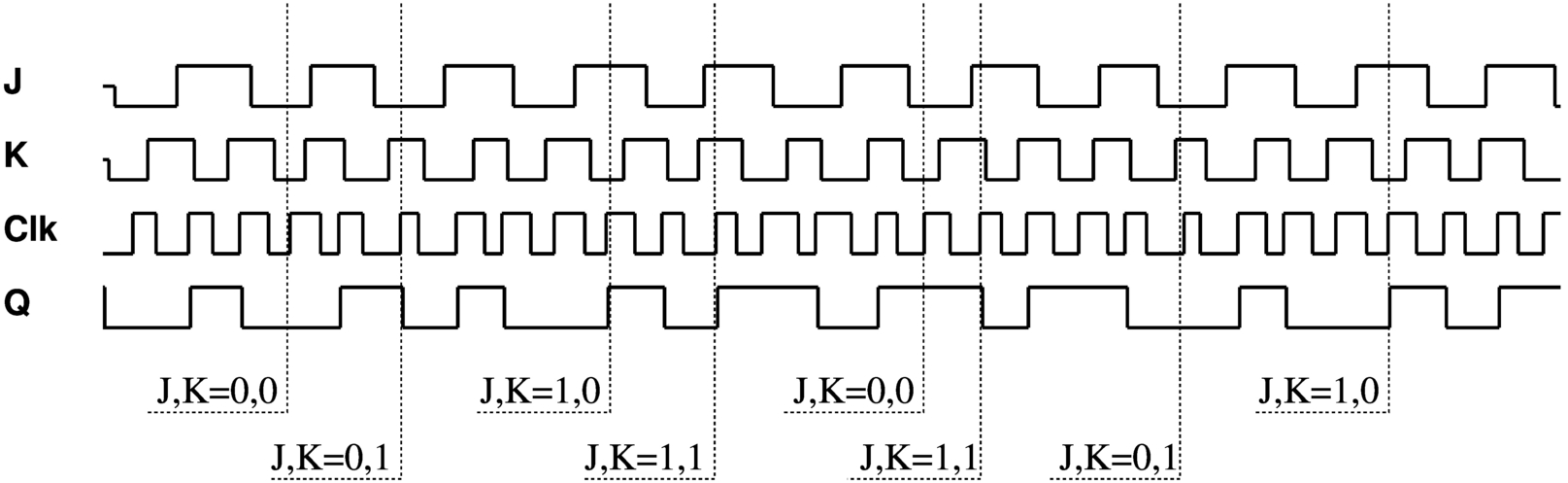

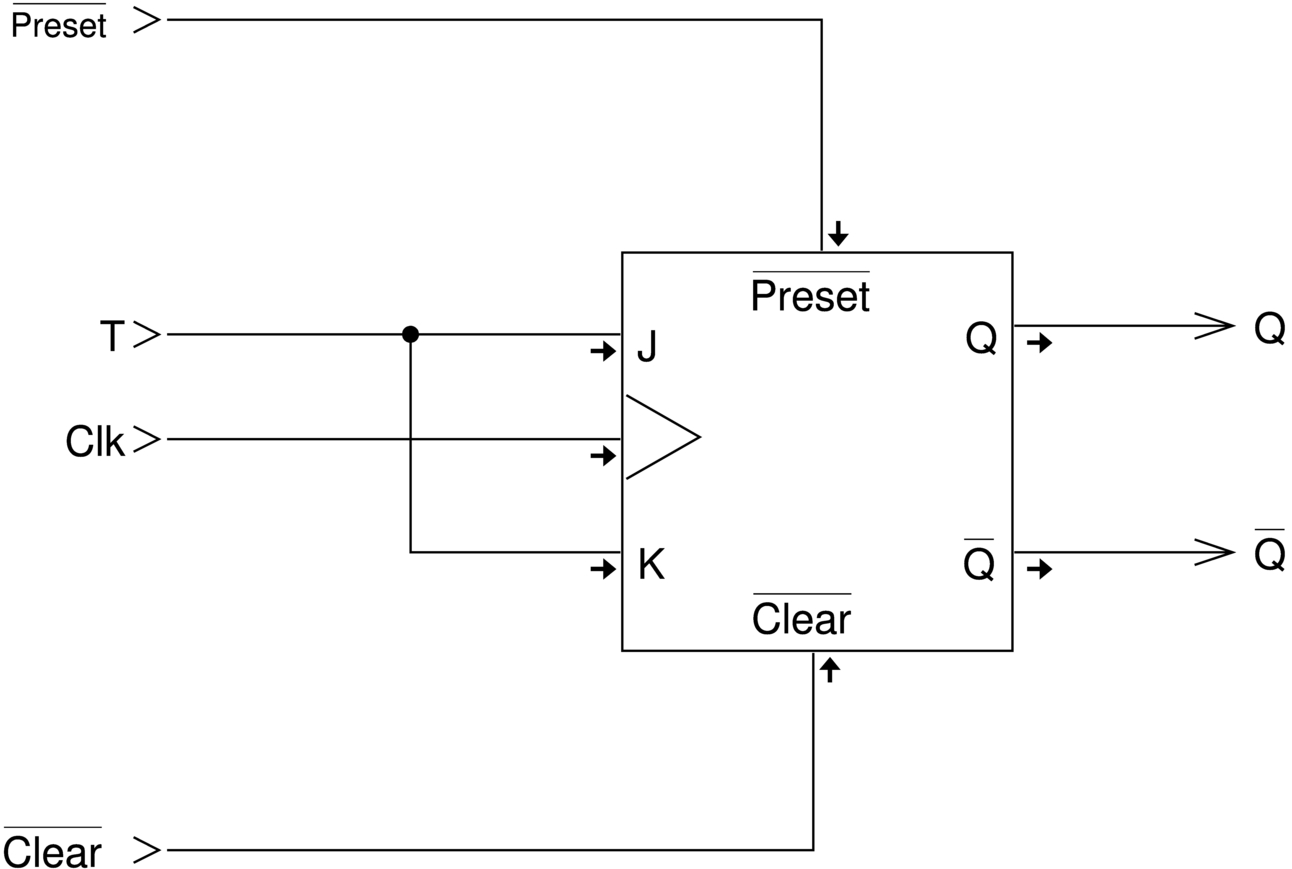

Flip-flop JK

Un'altra variante del flip-flop D, simile al flip-flop T, ma che richiama il funzionamento del flip-flop SR, è il flip-flop JK. Come per il flip-flop T, nella tabella della verità si usa la notazione Q(t) per indicare il valore dell'uscita Q nel momento t e la notazione Q(t+1) per indicare il valore dell'uscita Q nel momento successivo t+1, corrispondente all'impulso di clock successivo.

|

Figura u129.29. Simbolo del flip-flop JK, tabella della verità e tracciato. Si osservi che gli ingressi J e K si comportano in modo analogo a gli ingressi S e R di un flip-flop SR, con la differenza che l'attivazione di entrambi provoca solo lo scambio dei valori delle uscite, senza altre complicazioni.

|

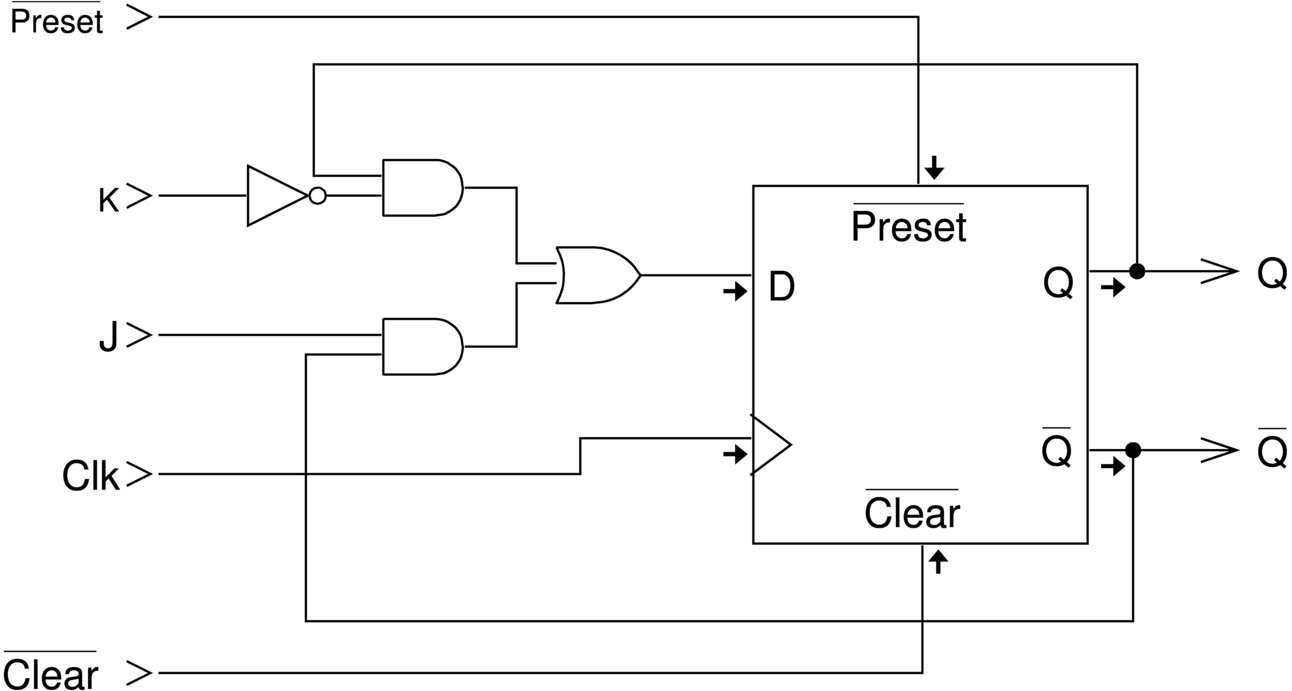

Per realizzare il flip-flop JK è necessario tenere in considerazione il fatto che inizialmente non si conosce lo stato delle uscite, quindi è importante poter azzerare il flip-flop all'avvio. Dal momento che si tratta di estendere il flip-flop D, nella figura successiva si parte da quello che dispone degli ingressi di azzeramento e di impostazione.

|

Figura u129.30. Realizzazione del flip-flop JK, partendo da un flip-flop D, munito di ingressi di azzeramento e di impostazione. Questa realizzazione è da preferire rispetto a quella della figura successiva.

|

La figura successiva mostra una realizzazione diversa del flip-flop JK, tratta dal libro Digital Computer Electronics di Malvino e Brown, nel capitolo dedicato ai flip-flop. Tuttavia, attraverso l'uso di un simulatore, si determina che se gli ingressi J e K vengono attivati e disattivati simultaneamente, prima che ci sia la variazione negativa del clock, al momento della variazione negativa del clock si ottiene ugualmente lo scambio dei valori nelle uscite, mentre ciò non dovrebbe avvenire secondo lo schema di funzionamento previsto per un flip-flop JK.

|

Figura u129.31. Realizzazione del flip-flop JK, partendo da un flip-flop SR in cascata: in tal caso, l'impulso di clock ha effetto in corrispondenza del margine negativo (negative edge triggered). Bisogna però fare attenzione al fatto che l'attivazione e successiva disattivazione simultanea dei valori degli ingressi, prima della variazione negativa del clock, provoca lo scambio dei valori delle uscite, come se gli ingressi fossero ancora attivi in quel momento.

|

È evidente che disponendo di un flip-flop JK è possibile ottenere un flip-flop T, semplicemente unendo gli ingressi J e K che diventano così l'ingresso T.

|

Figura u129.32. Adattamento di un flip-flop JK per ottenere un flip-flop T.

|

«a2» 2013.11.11 --- Copyright © Daniele Giacomini -- appunti2@gmail.com http://informaticalibera.net